มีตระกูลลอจิกหลายประเภทที่ใช้ในการออกแบบวงจรลอจิกดิจิทัล ลอจิกทรานซิสเตอร์ตัวต้านทาน (RTL), ลอจิกคู่ของตัวส่งสัญญาณ (ECL), ลอจิกทรานซิสเตอร์ไดโอด (DTL), ลอจิกเซมิคอนดักเตอร์ออกไซด์ของโลหะประกอบ (CMOS) และ ทรานซิสเตอร์-ทรานซิสเตอร์ลอจิก (TTL) . จากตระกูลลอจิกเหล่านี้ ตระกูลลอจิก DTL ถูกใช้โดยทั่วไปก่อนทศวรรษ 1960 และ 1970 เพื่อแทนที่ตระกูลลอจิกขั้นสูงเพิ่มเติมเช่น ซีมอส และทีทีแอล ลอจิกไดโอด-ทรานซิสเตอร์เป็นคลาสของ วงจรดิจิตอล ที่ถูกออกแบบด้วยไดโอดและทรานซิสเตอร์ ดังนั้นการรวมกันของไดโอดและทรานซิสเตอร์ทำให้สามารถสร้างฟังก์ชันลอจิกที่ซับซ้อนด้วยส่วนประกอบที่ค่อนข้างเล็กได้ บทความนี้จะให้ข้อมูลโดยย่อเกี่ยวกับ ลอจิกทรานซิสเตอร์ DTL หรือไดโอด และการประยุกต์ของมัน

ลอจิกทรานซิสเตอร์ไดโอดคืออะไร?

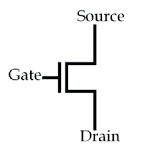

ลอจิกทรานซิสเตอร์ไดโอดเป็นวงจรลอจิกที่อยู่ในตระกูลลอจิกดิจิทัลซึ่งใช้ในการสร้างวงจรดิจิทัล วงจรนี้สามารถออกแบบได้ด้วย ไดโอด และทรานซิสเตอร์ที่ใช้ไดโอดที่ด้านอินพุต และใช้ทรานซิสเตอร์ที่ด้านเอาท์พุต จึงเรียกว่า DTL DTL เป็นคลาสเฉพาะของวงจรที่ใช้ในอุปกรณ์อิเล็กทรอนิกส์ดิจิทัลปัจจุบันสำหรับการประมวลผลสัญญาณไฟฟ้า

ในวงจรลอจิกนี้ ไดโอดมีประโยชน์ในการทำหน้าที่ลอจิก ในขณะที่ทรานซิสเตอร์ถูกใช้เพื่อทำหน้าที่ขยายสัญญาณ DTL มีประโยชน์มากมายเมื่อเทียบกับ ตัวต้านทาน ตรรกะของทรานซิสเตอร์เช่น ค่าการกระจายที่สูงกว่าและค่าเสียงรบกวนที่สูง ดังนั้น DTL จึงถูกแทนที่ด้วยตระกูล RTL ที่ ลักษณะเฉพาะของไดโอดทรานซิสเตอร์ลอจิก ส่วนใหญ่ได้แก่; ผู้ไร้วัฒนธรรมดิจิทัล นักยุทธศาสตร์ดิจิทัล สถาปนิกดิจิทัล ความคล่องตัวขององค์กร ลูกค้าเป็นศูนย์กลาง ผู้ให้การสนับสนุนข้อมูล นักจัดภูมิทัศน์สถานที่ทำงานดิจิทัล และเครื่องมือเพิ่มประสิทธิภาพกระบวนการทางธุรกิจ

วงจรลอจิกทรานซิสเตอร์ไดโอด

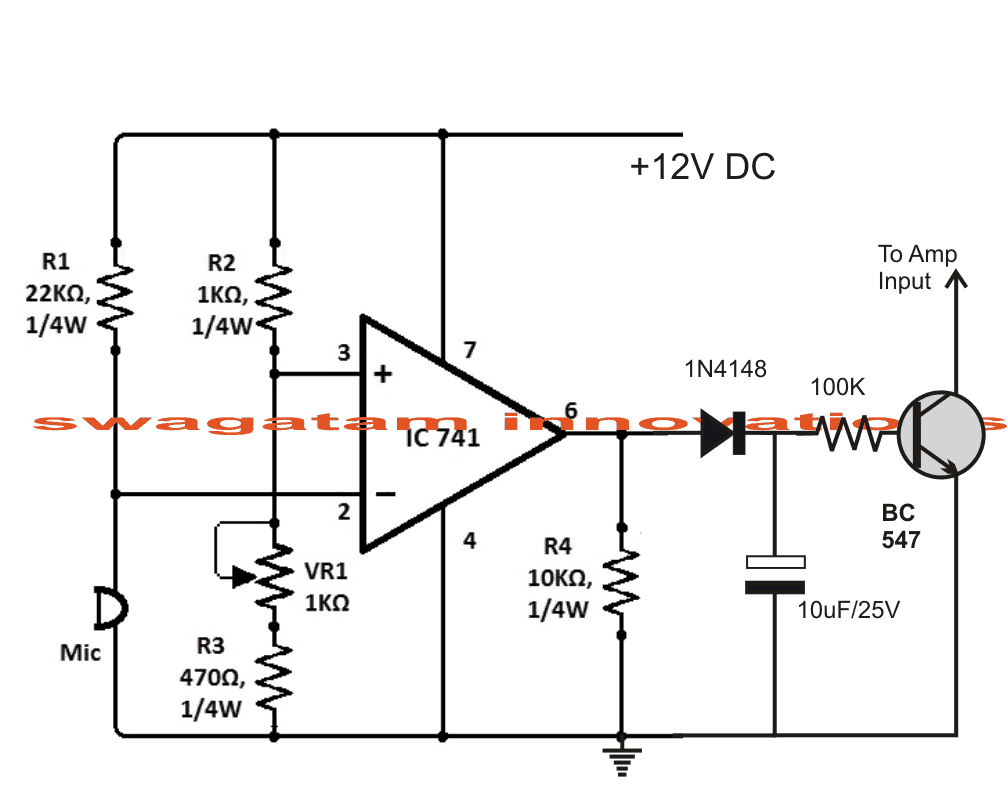

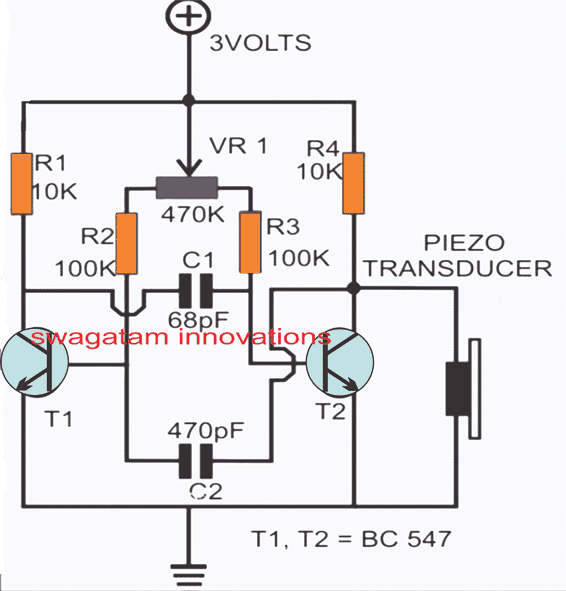

วงจรตรรกะของทรานซิสเตอร์ไดโอดแสดงอยู่ด้านล่าง นี่คือวงจรเกต NAND ลอจิกของทรานซิสเตอร์ไดโอดแบบสองอินพุต วงจรนี้ได้รับการออกแบบด้วยไดโอดสองตัวและทรานซิสเตอร์หนึ่งตัวโดยที่ไดโอดสองตัวระบุด้วย D1 และ D2 และตัวต้านทานจะถูกระบุด้วย R1 ซึ่งสร้างด้านอินพุตของวงจรลอจิก การกำหนดค่า CE ของทรานซิสเตอร์ Q1 และตัวต้านทาน R2 สร้างด้านเอาต์พุต ตัวเก็บประจุ 'C1' ในวงจรนี้ใช้เพื่อให้กระแสโอเวอร์ไดรฟ์ตลอดระยะเวลาการสวิตชิ่ง ซึ่งจะทำให้เวลาในการสวิตชิ่งลดลงเหลือบางระดับ

ลอจิกทรานซิสเตอร์ไดโอดทำงาน

เมื่อใดก็ตามที่อินพุตทั้งสองของวงจร A & B ต่ำ ไดโอด D1 และ D2 ทั้งสองจะมีความลำเอียงไปข้างหน้า ดังนั้นไดโอดเหล่านี้จะเคลื่อนที่ไปในทิศทางไปข้างหน้า ดังนั้นการจ่ายกระแสเนื่องจากแรงดันไฟฟ้า (+VCC = 5V) จะจ่ายให้กับ GND ตลอดทั้งตัวต้านทาน R1 และไดโอดสองตัว แหล่งจ่ายแรงดันไฟฟ้าจะลดลงภายในตัวต้านทาน R1 และไม่เพียงพอสำหรับการเปิดทรานซิสเตอร์ Q1 ดังนั้นทรานซิสเตอร์ Q1 จะอยู่ในโหมดตัดการทำงาน ดังนั้น o/p ที่เทอร์มินัล 'Y' จะเป็นลอจิก 1 หรือค่าสูง

เมื่ออินพุตตัวใดตัวหนึ่งมีค่าต่ำ ไดโอดที่เกี่ยวข้องจะเอนเอียงไปข้างหน้า ดังนั้นการดำเนินการที่คล้ายกันจะเกิดขึ้น เนื่องจากไดโอดตัวใดตัวหนึ่งมีความเอนเอียงไปข้างหน้า กระแสไฟฟ้าจะถูกส่งไปยังกราวด์ตลอดทั้งไดโอดที่มีไบแอสไปข้างหน้า ดังนั้นทรานซิสเตอร์ 'Q1' จะอยู่ในโหมดตัดการเชื่อมต่อ ดังนั้นเอาต์พุตที่เทอร์มินัล 'Y' จะเป็น สูงหรือตรรกะ 1.

เมื่อใดก็ตามที่อินพุต A และ B ทั้งสองมีค่าสูง ไดโอดทั้งสองจะมีอคติย้อนกลับ ดังนั้นไดโอดทั้งสองจะไม่ทำงาน ดังนั้นในสภาวะนี้ แรงดันไฟฟ้าจากแหล่งจ่าย +VCC จะเพียงพอที่จะขับเคลื่อนทรานซิสเตอร์ Q1 เข้าสู่โหมดการนำไฟฟ้า

ดังนั้นทรานซิสเตอร์จึงดำเนินการตลอดขั้วตัวปล่อยและตัวสะสม แรงดันไฟฟ้าทั้งหมดจะลดลงภายในตัวต้านทาน 'R2' และเอาต์พุตที่เทอร์มินัล 'Y' จะมีค่าต่ำ o/p และถือว่าต่ำหรือตรรกะ 0

ตารางความจริง

ตารางความจริง DTL แสดงอยู่ด้านล่าง

|

ก |

บี | และ |

|

0 |

0 | 1 |

|

0 |

1 |

1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

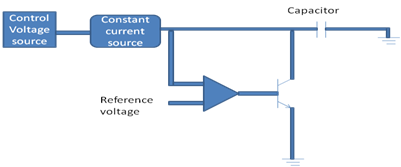

ความล่าช้าในการแพร่กระจายตรรกะของทรานซิสเตอร์ไดโอดมีขนาดค่อนข้างใหญ่ เมื่อใดก็ตามที่อินพุตทั้งหมดมีลอจิกสูง ทรานซิสเตอร์จะเข้าสู่ภาวะอิ่มตัวและสะสมประจุภายในบริเวณฐาน เมื่อใดก็ตามที่อินพุตหนึ่งค่าต่ำ ประจุนี้ควรถูกลบออก เพื่อเปลี่ยนเวลาการแพร่กระจาย ในการเร่งความเร็วตรรกะของทรานซิสเตอร์ไดโอดในเทคนิคทางเดียวคือการเพิ่มตัวเก็บประจุข้ามตัวต้านทาน R3 ที่นี่ตัวเก็บประจุนี้ช่วยในการปิดทรานซิสเตอร์โดยกำจัดประจุสะสมที่ขั้วฐาน ตัวเก็บประจุในวงจรนี้ยังช่วยในการเปิดทรานซิสเตอร์ด้วยการเพิ่มประสิทธิภาพของไดรฟ์ฐานตัวแรก

ลอจิกทรานซิสเตอร์ไดโอดดัดแปลง

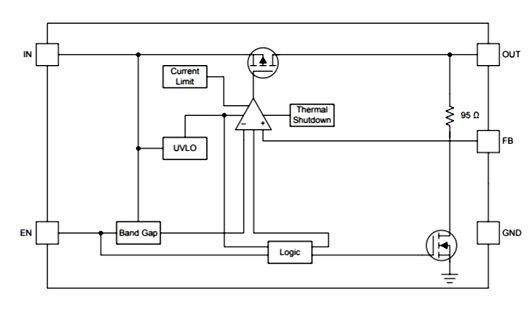

เกท DTL NAND ที่แก้ไขแล้วแสดงอยู่ด้านล่าง ค่าขนาดใหญ่ของส่วนประกอบตัวต้านทานและตัวเก็บประจุนั้นยากมากที่จะประดิษฐ์บนไอซีในเชิงเศรษฐกิจ ดังนั้นวงจรเกต DTL NAND ต่อไปนี้สามารถปรับเปลี่ยนเพื่อการใช้งาน IC ได้โดยเพียงแค่กำจัดตัวเก็บประจุ C1 ออก ลดค่าของตัวต้านทาน & การใช้ ทรานซิสเตอร์ & ไดโอดทุกที่ที่ทำได้ วงจรดัดแปลงนี้ใช้แหล่งจ่ายไฟบวกเพียงตัวเดียว และวงจรนี้รวมระยะอินพุตที่มีไดโอด D1 และ D2 ตัวต้านทาน R3 และเกท AND ซึ่งต่อผ่านอินเวอร์เตอร์แบบทรานซิสเตอร์

การทำงาน

การทำงานของวงจรนี้คือ วงจรนี้มีขั้วอินพุต A และ B สองตัว และแรงดันไฟฟ้าอินพุตเช่น A & B อาจเป็นได้ทั้งสูงหรือต่ำ

หากอินพุต A & B ทั้งสองต่ำหรือตรรกะ 0 ไดโอดทั้งสองจะเอนเอียงไปข้างหน้า ดังนั้นศักยภาพที่ 'M' คือแรงดันตกคร่อมของไดโอดหนึ่งตัวที่ 0.7 V แม้ว่าจะขับทรานซิสเตอร์ 'Q' เข้าสู่การนำ จากนั้นเราต้องใช้ 2.1 V เพื่อส่งต่อไบแอสไดโอด D3, D4 และทางแยก BE ของทรานซิสเตอร์ 'Q' ดังนั้นทรานซิสเตอร์นี้คือตัวตัดและให้เอาต์พุต Y = 1

Y = Vcc = ลอจิก 1 และสำหรับ A = B = 0, Y = 1 หรือสูง

หากอินพุตตัวใดตัวหนึ่ง A หรือ B ต่ำ อินพุตตัวใดตัวหนึ่งสามารถเชื่อมต่อกับ GND ด้วยเทอร์มินัลใดๆ ที่เชื่อมต่อกับ +Vcc ไดโอดที่เทียบเท่าจะดำเนินการ และทรานซิสเตอร์ VM ≅ 0.7 V & Q จะถูกตัดออก และระบุเอาต์พุต 'Y' = 1 หรือลอจิก High

ถ้า A = 0 & B =1 (หรือ) ถ้า A = 1 & B = 0 ดังนั้นเอาต์พุต Y = 1 หรือสูง

หากอินพุตสองตัวเช่น A & B ทั้งคู่มีค่าสูงและ A & B ทั้งสองเชื่อมต่อกับ + Vcc ดังนั้นไดโอด D1 และ D2 ทั้งสองจะเป็นแบบย้อนกลับและจะไม่ดำเนินการ ไดโอด D3 และ D4 มีไบแอสไปข้างหน้า และกระแสที่เทอร์มินัลฐานจะจ่ายให้กับทรานซิสเตอร์ Q ผ่าน Rd, D3 และ D4 ทรานซิสเตอร์สามารถขับเคลื่อนไปสู่ความอิ่มตัวและแรงดันไฟฟ้า o/p จะเป็นแรงดันไฟฟ้าต่ำ

สำหรับ A = B = 1 เอาต์พุต Y = 0 หรือ LOW

การใช้งาน DTL ที่แก้ไขมีดังต่อไปนี้

สามารถกระจายพัดลมออกได้มากขึ้นเนื่องจากเกตต่อมามีอิมพีแดนซ์สูงโดยมีเงื่อนไขลอจิกสูง วงจรนี้มีการป้องกันเสียงรบกวนที่เหนือกว่า การใช้ไดโอดหลายตัวแทนตัวต้านทานและตัวเก็บประจุจะทำให้วงจรนี้ประหยัดมากเมื่ออยู่ในรูปแบบวงจรรวม

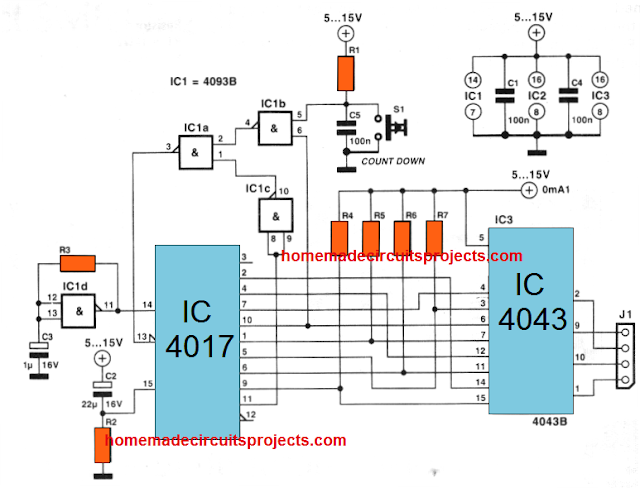

ไดโอดทรานซิสเตอร์ลอจิก NOR Gate

เกต NOR ลอจิกของทรานซิสเตอร์ไดโอดได้รับการออกแบบคล้ายกับเกต DTL NAND ที่มีเกท DRL OR พร้อมอินเวอร์เตอร์ทรานซิสเตอร์ วงจร DTL NOR สามารถออกแบบได้หรูหรายิ่งขึ้นโดยเพียงแค่รวมอินเวอร์เตอร์ DTL ต่างๆ เข้าด้วยกันผ่านเอาต์พุตทั่วไป ในลักษณะนี้ อินเวอร์เตอร์หลายตัวสามารถรวมเข้าด้วยกันเพื่อให้อินพุตที่จำเป็นสำหรับเกท NOR

วงจรนี้สามารถออกแบบได้ด้วยส่วนประกอบของวงจร DTL Inverter นอกเหนือจาก แหล่งจ่ายไฟ & สอง 4.7 เค ตัวต้านทาน , 1N914 หรือ 1N4148 ไดโอดซิลิคอน เชื่อมต่อวงจรตามวงจรที่แสดงด้านล่าง

การทำงาน

เมื่อทำการเชื่อมต่อแล้ว จำเป็นต้องจ่ายไฟให้กับวงจร หลังจากนั้น ให้ใช้การผสมอินพุตที่เป็นไปได้สี่แบบที่ A & B จากแหล่งจ่ายไฟด้วยสวิตช์ดิป ตอนนี้สำหรับทุกอินพุตรวมกัน จำเป็นต้องจดบันทึกเงื่อนไขลอจิกของเอาต์พุต 'Q' ตามที่แสดงด้วย นำ & บันทึกผลลัพธ์นั้น เปรียบเทียบผลลัพธ์กับการทำงานของเกต NOR เมื่อคุณสังเกตเสร็จแล้ว ให้ปิดแหล่งจ่ายไฟ

|

ก |

บี |

Y = (เอ+บี)’ |

|

0 |

0 | 1 |

|

0 |

1 | 0 |

| 1 | 0 |

0 |

| 1 | 1 |

0 |

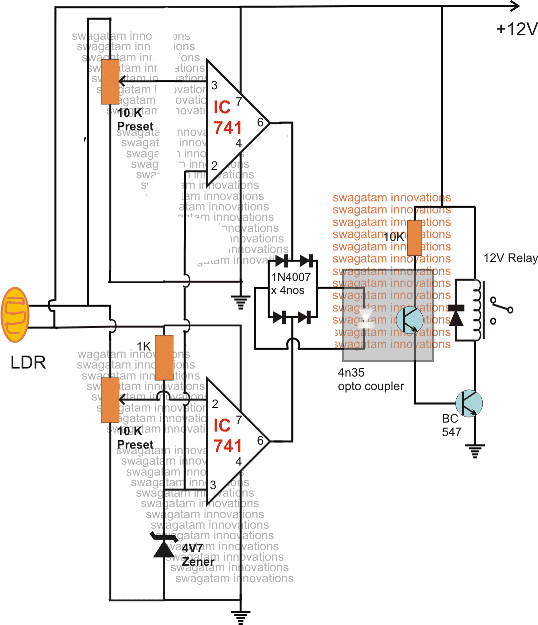

ลอจิกทรานซิสเตอร์ไดโอดและเกต

ตรรกะและเกทของทรานซิสเตอร์ไดโอดแสดงอยู่ด้านล่าง ในวงจรนี้ ตรรกะจะระบุดังนี้ 1 & 0 ถือเป็นตรรกะเชิงบวก +5V และ 0V ตามลำดับ

เมื่อใดก็ตามที่อินพุตใดๆ จาก A1, A2 (หรือ) A3 อยู่ในสถานะลอจิกต่ำ ไดโอดที่เชื่อมต่อกับอินพุตนั้นจะมีอคติไปข้างหน้าหลังจากนั้น ทรานซิสเตอร์จะถูกตัดออก และเอาต์พุตจะต่ำหรือตรรกะ 0 ในทำนองเดียวกันหากอินพุตทั้งสามอยู่ที่ลอจิก 1 แสดงว่าไดโอดและทรานซิสเตอร์ไม่ดำเนินการหนัก หลังจากนั้นทรานซิสเตอร์จะอิ่มตัวและเอาต์พุตจะเป็นสูงหรือลอจิก 1

ตารางความจริงของตรรกะและเกตของทรานซิสเตอร์ไดโอดแสดงอยู่ด้านล่าง

|

A1 |

A2 | A3 |

Y = เอบี |

|

0 |

0 | 0 | 0 |

|

0 |

0 | 1 | 0 |

|

0 |

1 | 0 |

0 |

| 0 | 1 | 1 |

0 |

|

1 |

0 | 0 | 0 |

|

1 |

0 | 1 |

0 |

| 1 | 1 | 0 |

0 |

| 1 | 1 | 1 |

1 |

การเปรียบเทียบระหว่าง DTL, TTL และ RTL

ความแตกต่างระหว่าง DTL, TTL และ RTL มีอธิบายไว้ด้านล่าง

| ดีทีแอล | ทีทีแอล |

ร.ต.ท |

| คำว่า DTL ย่อมาจาก Diode-Transistor Logic | คำว่า TTL ย่อมาจาก Transistor-Transistor Logic | คำว่า RTL ย่อมาจาก Resistor-Transistor Logic |

| ใน DTL ลอจิกเกตได้รับการออกแบบให้มีไดโอดและทรานซิสเตอร์จุดเชื่อมต่อ PN | ใน TTL ลอจิกเกตได้รับการออกแบบด้วย BJT

|

ใน RTL ลอจิกเกตได้รับการออกแบบให้มีตัวต้านทานและทรานซิสเตอร์ |

| ใน DTL ไดโอดถูกใช้เป็นส่วนประกอบ i/p และทรานซิสเตอร์ถูกใช้เป็นส่วนประกอบ o/p | ใน TTL จะใช้ทรานซิสเตอร์ตัวหนึ่งสำหรับการขยายในขณะที่ทรานซิสเตอร์อีกตัวหนึ่งใช้สำหรับการสลับ | ตัวต้านทานใน RTL ถูกใช้เป็นส่วนประกอบ i/p และทรานซิสเตอร์ถูกใช้เป็นส่วนประกอบ o/p |

| การตอบสนอง DTL นั้นดีกว่าเมื่อเปรียบเทียบกับ RTL | การตอบสนองแบบ TTL นั้นดีกว่า DTL และ RTL มาก | การตอบสนอง RTL ช้า |

| การสูญเสียพลังงานต่ำ | มีการสูญเสียพลังงานต่ำมาก | การสูญเสียพลังงานมีสูง |

| การก่อสร้างมีความซับซ้อน | การก่อสร้างนั้นง่ายมาก | การก่อสร้างนั้นเรียบง่าย |

| Fanout ขั้นต่ำของ DTL คือ 8 | TTL fanout ขั้นต่ำคือ 10 | Fanout ขั้นต่ำของ RTL คือ 5 |

| โดยทั่วไปการกระจายพลังงานสำหรับแต่ละเกตคือ 8 ถึง 12 mW | โดยทั่วไปการกระจายพลังงานสำหรับแต่ละเกตจะอยู่ที่ 12 ถึง 22 mW | โดยทั่วไปการกระจายพลังงานสำหรับแต่ละเกตคือ 12 mW |

| ภูมิคุ้มกันทางเสียงของมันดี | ภูมิคุ้มกันทางเสียงของมันดีมาก | ภูมิคุ้มกันทางเสียงอยู่ในระดับปานกลาง |

| ความล่าช้าในการแพร่กระจายโดยทั่วไปสำหรับเกตคือ 30 ns | ความล่าช้าในการแพร่กระจายโดยทั่วไปสำหรับเกตคือ 12 ถึง 6 ns | ความล่าช้าในการแพร่กระจายโดยทั่วไปสำหรับเกตคือ 12 ns |

| อัตรานาฬิกาของมันคือ 12 ถึง 30 MHZ | อัตรานาฬิกาของมันคือ 15 ถึง 60 MHZ | อัตรานาฬิกาของมันคือ 8 MHZ |

| มีจำนวนฟังก์ชันที่ค่อนข้างสูง | มีจำนวนฟังก์ชันที่สูงมาก | มีฟังก์ชันจำนวนมาก |

| ตรรกะ DTL ใช้ในการสวิตชิ่งพื้นฐานและวงจรดิจิตอล | ตรรกะ TTL ใช้ในวงจรดิจิตอลและวงจรรวมสมัยใหม่ | RTL ถูกใช้ในคอมพิวเตอร์เครื่องเก่า |

ข้อดี

ข้อดีของวงจรลอจิกทรานซิสเตอร์ไดโอดมีดังต่อไปนี้

- ความเร็วในการเปลี่ยนของ DTL นั้นเร็วกว่าเมื่อเปรียบเทียบกับ RTL

- การใช้ไดโอดภายในวงจร DTL ทำให้ราคาถูกลงเนื่องจากการประดิษฐ์ไดโอดบนไอซีนั้นง่ายกว่าเมื่อเทียบกับตัวต้านทานและตัวเก็บประจุ

- การสูญเสียพลังงานภายในวงจร DTL ต่ำมาก

- วงจร DTL มีความเร็วในการสลับที่เร็วกว่า

- DTL มีการกระจายสัญญาณออกที่มากขึ้นและมีเสียงรบกวนที่ดีขึ้น

ที่ ข้อเสียของวงจรลอจิกทรานซิสเตอร์ไดโอด รวมสิ่งต่อไปนี้

- DTL มีความเร็วการทำงานต่ำเมื่อเปรียบเทียบกับ TTL

- มีความล่าช้าในการแพร่กระจายของเกตที่มีขนาดใหญ่มาก

- สำหรับอินพุตสูง เอาท์พุตของ DTL จะเข้าสู่ภาวะอิ่มตัว

- ทำให้เกิดความร้อนตลอดการทำงาน

การใช้งาน

ที่ การประยุกต์ตรรกะของทรานซิสเตอร์ไดโอด รวมสิ่งต่อไปนี้

- ไดโอด- ทรานซิสเตอร์ลอจิก ใช้เพื่อออกแบบและสร้างวงจรดิจิทัลที่ไหน ประตูลอจิก ใช้ไดโอดภายในระยะอินพุตและ BJT ที่ระยะเอาต์พุต

- DTL เป็นวงจรประเภทเฉพาะที่ใช้ในอุปกรณ์อิเล็กทรอนิกส์ดิจิทัลในปัจจุบันเพื่อประมวลผลสัญญาณไฟฟ้า

- DTL ใช้เพื่อสร้างวงจรลอจิกอย่างง่าย

อย่างนี้นี่เอง ภาพรวมของตรรกะของทรานซิสเตอร์ไดโอด วงจร การทำงาน ข้อดี ข้อเสีย และการประยุกต์ วงจร DTL มีความซับซ้อนมากกว่าเมื่อเปรียบเทียบกับวงจร RTL แต่ตรรกะนี้ได้เปลี่ยนแปลง RTL เนื่องจากความสามารถ FAN OUT ที่เหนือกว่าและขอบเขตเสียงรบกวนที่เพิ่มขึ้น แต่ DTL มีความเร็วต่ำ นี่คือคำถามสำหรับคุณ RTL คืออะไร?