ในชีวิตประจำวันของเราเราใช้เพื่อสื่อสารกับผู้อื่นบ่อยครั้งโดยใช้หลายประเภท ระบบการสื่อสาร . ระบบการสื่อสารนี้สามารถแบ่งออกเป็นประเภทต่างๆเช่นระบบวิทยุสื่อสารระบบโทรคมนาคม ระบบสื่อสารไร้สาย , ระบบสื่อสารด้วยแสงและอื่น ๆ เพื่อให้ระบบการสื่อสารเหล่านี้ทำงานได้อย่างมีประสิทธิภาพเราจำเป็นต้องมีระบบควบคุมบางอย่างเช่น Phase-lock loop, Cooperative control, Networked control เป็นต้น

Phase-Locked Loop (PLL) คืออะไร?

เฟสล็อกลูปใช้เป็นระบบควบคุมเพื่อควบคุมการทำงานที่แตกต่างกันในระบบสื่อสารคอมพิวเตอร์และหลาย ๆ การใช้งานอิเล็กทรอนิกส์ . ใช้เพื่อสร้างสัญญาณเอาต์พุตซึ่งมีเฟสที่เกี่ยวข้องกับเฟสสัญญาณอินพุต

PLL มีหลายประเภทเช่น Analog หรือ Linear PLL, Digital PLL, Software PLL, Neuronal PLL และ PLL ดิจิทัลทั้งหมด

เฟสล็อคลูปการทำงาน

ในระบบการสื่อสารการทำงานของ PLL สามารถอธิบายได้โดยการพิจารณา ระบบอนาล็อกและดิจิตอล .

อนาล็อกเฟสล็อคลูปในระบบการสื่อสาร

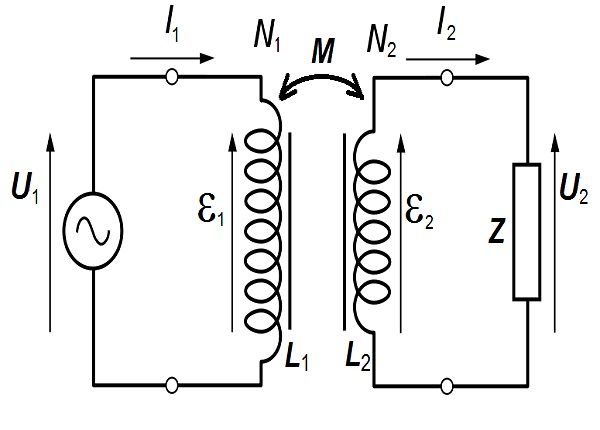

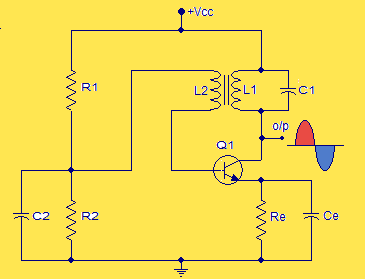

โดยทั่วไปแล้ว PLL เป็นรูปแบบของเซอร์โวลูปและ PLL พื้นฐานประกอบด้วยองค์ประกอบหลักสามส่วน ได้แก่ ตัวเปรียบเทียบเฟส / ตัวตรวจจับตัวกรองลูปและ ออสซิลเลเตอร์ควบคุมแรงดันไฟฟ้า .

เฟสล็อคลูป

แนวคิดหลักที่อยู่เบื้องหลังการทำงานของ PPL คือการเปรียบเทียบเฟสของสัญญาณสองสัญญาณ (โดยทั่วไปจะเปรียบเทียบเฟสสัญญาณอินพุตและเอาต์พุต) ดังนั้นความแตกต่างของเฟสระหว่างสัญญาณอินพุตและเอาต์พุตสามารถใช้เพื่อควบคุมความถี่ลูป แม้ว่าการวิเคราะห์ทางคณิตศาสตร์จะซับซ้อนมาก แต่การทำงานของ PLL นั้นง่ายมาก

ในระบบการสื่อสารหลายระบบ PLL ถูกใช้เพื่อวัตถุประสงค์ที่แตกต่างกัน:

- สำหรับติดตามเฟสหรือ การมอดูเลตความถี่ ใช้เป็น Demodulator

- เพื่อติดตามหรือซิงโครไนซ์สัญญาณทั้งสองที่มีความถี่ต่างกัน

- เพื่อลบเสียงรบกวนขนาดใหญ่จากสัญญาณขนาดเล็ก

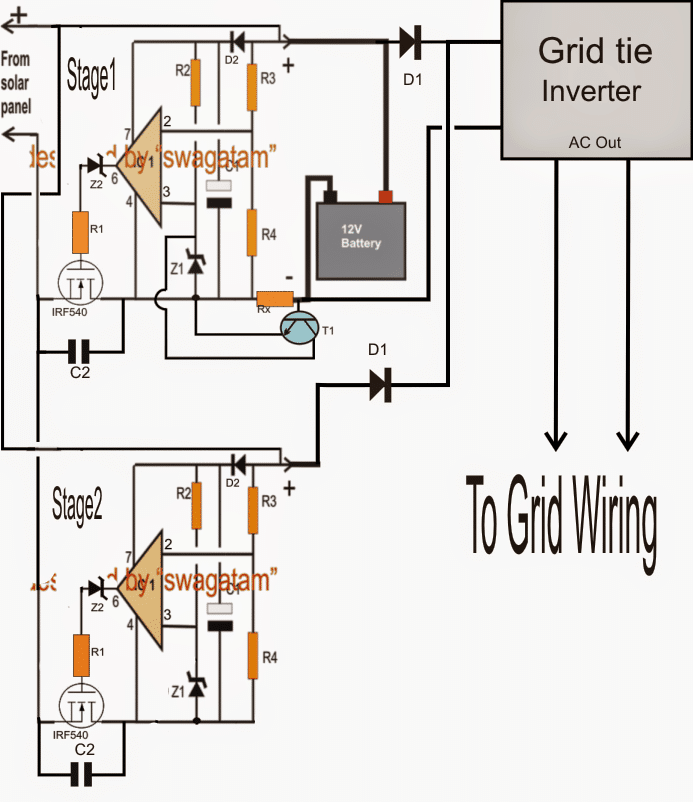

รูปด้านล่างแสดง PLL พื้นฐานซึ่งประกอบด้วย Phase Detector, Voltage Controlled Oscillator (VCO), Loop Filter

ออสซิลเลเตอร์ที่ควบคุมด้วยแรงดันไฟฟ้าของ PLL จะสร้างสัญญาณและสัญญาณนี้จาก VCO จะถูกส่งไปยังเครื่องตรวจจับเฟส เครื่องตรวจจับเฟสจะเปรียบเทียบสัญญาณนี้กับสัญญาณอ้างอิงและทำให้เกิดแรงดันไฟฟ้าผิดพลาดหรือแรงดันไฟฟ้าที่แตกต่างกัน สัญญาณข้อผิดพลาดของเครื่องตรวจจับเฟสนี้ถูกป้อนไปยังตัวกรองความถี่ต่ำสำหรับการลบองค์ประกอบความถี่สูงของสัญญาณหากมีและสำหรับการควบคุมคุณสมบัติหลายอย่างของลูป จากนั้นเอาต์พุตของตัวกรองลูปจะถูกป้อนเพื่อจ่ายแรงดันไฟฟ้าสำหรับขั้วควบคุมของออสซิลเลเตอร์ควบคุมแรงดันไฟฟ้า

การเปลี่ยนแปลงของแรงดันไฟฟ้าที่ปรับแต่งนี้ได้รับการตรวจจับเพื่อลดความแตกต่างของเฟสระหว่างสัญญาณทั้งสอง (อินพุตและเอาต์พุต) ดังนั้นความถี่ระหว่างสัญญาณทั้งสอง ในขั้นต้น PLL ไม่ล็อคและแรงดันไฟฟ้าผิดพลาดจะลากความถี่ VCO ไปยังการอ้างอิงจนกว่าข้อผิดพลาดจะไม่สามารถลดลงได้อีกจากนั้นลูปจะถูกล็อค

ข้อผิดพลาดที่แท้จริงระหว่างสัญญาณทั้งสอง (อินพุตและเอาต์พุต) จะลดลงเหลือเพียงเล็กน้อย ใช้เครื่องขยายเสียง ระหว่างออสซิลเลเตอร์ควบคุมแรงดันไฟฟ้าและเครื่องตรวจจับเฟส หาก PLL ถูกล็อคจะเกิดแรงดันไฟฟ้าผิดพลาดคงที่ แรงดันไฟฟ้าผิดพลาดในสถานะคงที่นี้แสดงว่าไม่มีการเปลี่ยนแปลงความแตกต่างของเฟสระหว่างสัญญาณอ้างอิงและ VCO ดังนั้นเราสามารถพูดได้ว่าความถี่ของสัญญาณทั้งสอง (สัญญาณอินพุตและเอาต์พุต) เท่ากันทุกประการ

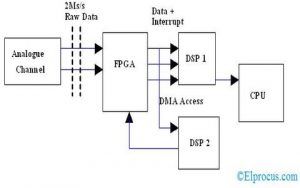

Digital Phase Locked Loop ในระบบการสื่อสาร

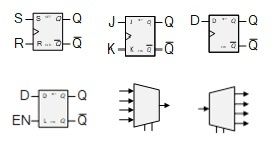

โดยทั่วไปแล้ว PLL แบบอะนาล็อกประกอบด้วยเครื่องตรวจจับเฟสอะนาล็อกออสซิลเลเตอร์ควบคุมแรงดันไฟฟ้าและตัวกรองความถี่ต่ำ ในทำนองเดียวกันลูปล็อกเฟสดิจิทัลประกอบด้วยตัวตรวจจับเฟสดิจิตอลก ทะเบียนกะอนุกรม สัญญาณนาฬิกาท้องถิ่นที่เสถียร

ลูปล็อคเฟสดิจิตอล

ตัวอย่างอินพุตดิจิทัลถูกดึงออกมาจากสัญญาณที่ได้รับและตัวอย่างเหล่านี้จะได้รับโดยการลงทะเบียนกะอนุกรมซึ่งขับเคลื่อนด้วยพัลส์นาฬิกาที่ให้มาจากสัญญาณนาฬิกาท้องถิ่น วงจร Phase-corrector ที่รับสัญญาณนาฬิกาในพื้นที่ใช้เพื่อสร้างสัญญาณนาฬิกาที่เสถียรในเฟสใหม่พร้อมกับสัญญาณที่ได้รับโดยการปรับเฟสช้าเพื่อให้ตรงกับเฟสสัญญาณที่ได้รับ

การปรับแต่งนี้สามารถทำได้ตามตัวอย่างความเร็วสูงของแต่ละบิตโดยใช้ตรรกะการแก้ไข ตัวอย่างสัญญาณที่ได้รับจากการสุ่มตัวอย่างของสัญญาณที่ได้รับด้วยความเร็วสัญญาณนาฬิกาท้องถิ่นจะอยู่ในทะเบียนกะ

สามารถตรวจจับการปรับเฟสที่ต้องการได้โดยสังเกตจากชุดตัวอย่างของสัญญาณที่ได้รับ นาฬิกาสองเรือนถูกกล่าวว่าอยู่ในเฟสก็ต่อเมื่อศูนย์กลางของบิตที่ได้รับอยู่ที่กึ่งกลางของทะเบียนกะ ตัวปรับเฟสมีจุดมุ่งหมายเพื่อชดเชยหากนาฬิกาที่สร้างใหม่ล่าช้าหรือนำไปสู่สัญญาณอ้างอิง

การประยุกต์ใช้ Phase Locked Loop

- PLL มักใช้เพื่อจุดประสงค์ในการซิงโครไนซ์และสำหรับการซิงโครไนซ์บิตการซิงโครไนซ์สัญลักษณ์การแยกสัญญาณที่สอดคล้องกันและการขยายขีด จำกัด ในการสื่อสารในอวกาศ

- สัญญาณมอดูเลตความถี่สามารถ demodulated โดยใช้ PLL

- ความถี่ใหม่ซึ่งเป็นความถี่อ้างอิงหลายค่าใน เครื่องส่งวิทยุสื่อสาร และสังเคราะห์โดยการรักษาเสถียรภาพของความถี่อ้างอิงด้วยความถี่ใหม่สามารถทำได้โดย PLL

- มีแอปพลิเคชั่นมากมายสำหรับ PLL ในระบบสื่อสารคอมพิวเตอร์และอีกมากมาย วงจรอิเล็กทรอนิกส์ .

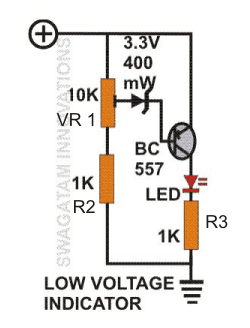

- แอปพลิเคชันด้านล่างของ PLL อธิบายถึงการใช้งาน PLL เป็นแรงดันไฟฟ้า ตัวแปลงความถี่ .

ตัวแปลงแรงดันเป็นความถี่ (VFC) โดยใช้ PLL

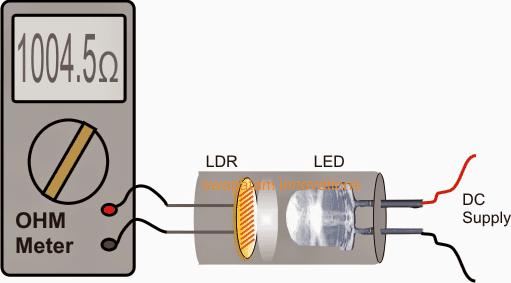

ในระบบการสื่อสารจำเป็นต้องส่งสัญญาณ (พิจารณาสัญญาณแอนะล็อกที่นี่) ไปยังระยะทางไกลด้วยความแม่นยำเต็มที่ เพื่อจุดประสงค์นี้จึงใช้ตัวแปลงแรงดันไฟฟ้าเป็นความถี่เนื่องจากง่ายต่อการส่งสัญญาณความถี่โดยไม่ก่อให้เกิดการรบกวนใด ๆ ในระยะทางไกลโดยใช้ตัวแยกแสงสายโคแอกเชียลหรือคู่บิดเกลียวลิงค์วิทยุ ลิงค์ใยแก้วนำแสง .

ตัวแปลงแรงดันไฟฟ้าเป็นความถี่มีสองประเภทคือ ประเภทมัลติไวเบรเตอร์ VFC และประเภทยอดดุลของประจุ VFC

มัลติไวเบรเตอร์ประเภท VFC

มัลติไวเบรเตอร์ VFC

ในมัลติไวเบรเตอร์ชนิด VFC ตัวเก็บประจุจะถูกชาร์จและคายประจุโดยใช้กระแสที่ได้จากแรงดันไฟฟ้าอินพุต อินพุตอ้างอิงที่เสถียรถูกกำหนดให้เพื่อตั้งค่าขีด จำกัด การสลับและความถี่เอาต์พุตเป็นสัดส่วนกับแรงดันไฟฟ้าขาเข้าและมีอัตราส่วนพื้นที่เครื่องหมายเอกภาพ

ประเภทยอดดุลของค่าธรรมเนียม VFC

ยอดดุล VFC

VFC ยอดดุลประจุประกอบด้วย Integrator ตัวเปรียบเทียบและแหล่งที่มาของค่าใช้จ่ายที่แม่นยำเมื่อใดก็ตามที่อินพุตถูกมอบให้กับอินทิเกรเตอร์จะถูกเรียกเก็บเงินและหากเอาต์พุตของอินทิเกรเตอร์นี้ถึงเกณฑ์ตัวเปรียบเทียบแหล่งที่มาของประจุจะถูกทริกเกอร์และประจุคงที่ ถูกลบออกจากตัวรวม อัตราการลบประจุจะต้องเท่ากับอัตราที่ให้มาซึ่งแหล่งกำเนิดประจุที่กระตุ้นความถี่และอินพุตไปยังตัวรวมจะเป็นสัดส่วนซึ่งกันและกัน

ดังนั้นบทความนี้จะให้คำอธิบายสั้น ๆ เกี่ยวกับไฟล์ ระบบลูปล็อคเฟส ในระบบการสื่อสาร นอกจากนี้บทความนี้ยังสามารถขยายได้ทางเทคนิคตามคำแนะนำและข้อสงสัยของคุณ ดังนั้นคุณสามารถติดต่อเราเพื่อขอความช่วยเหลือด้านเทคนิคโดยโพสต์ความคิดเห็นของคุณด้านล่าง