เฟสล็อกลูป เป็นหนึ่งในบล็อกพื้นฐานในระบบอิเล็กทรอนิกส์สมัยใหม่ โดยทั่วไปจะใช้ในมัลติมีเดียการสื่อสารและในแอปพลิเคชันอื่น ๆ PLL มีสองประเภทที่แตกต่างกัน - เชิงเส้นและไม่เชิงเส้น การออกแบบที่ไม่เป็นเชิงเส้นเป็นเรื่องยากและซับซ้อนในการออกแบบในโลกแห่งความเป็นจริง แต่ทฤษฎีการควบคุมเชิงเส้นได้รับการจำลองอย่างดีใน PLL แบบอะนาล็อก PLL ได้พิสูจน์แล้วว่าแบบจำลองเชิงเส้นนั้นเพียงพอสำหรับการใช้งานอิเล็กทรอนิกส์ส่วนใหญ่

Phase-Locked Loop คืออะไร?

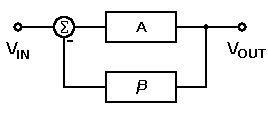

เฟสล็อกลูปประกอบด้วยตัวตรวจจับเฟสและออสซิลเลเตอร์ควบคุมแรงดันไฟฟ้า เอาต์พุตของเครื่องตรวจจับเฟสคืออินพุตของออสซิลเลเตอร์ที่ควบคุมแรงดันไฟฟ้า (VCO) และเอาต์พุตของ VCO เชื่อมต่อกับหนึ่งในอินพุตของเครื่องตรวจจับเฟสซึ่งแสดงไว้ด้านล่างในแผนภาพบล็อกพื้นฐาน เมื่ออุปกรณ์ทั้งสองนี้ป้อนซึ่งกันและกันรูปแบบลูป

แผนภาพพื้นฐานของเฟสล็อคลูป

แผนภาพบล็อกและหลักการทำงานของ PLL

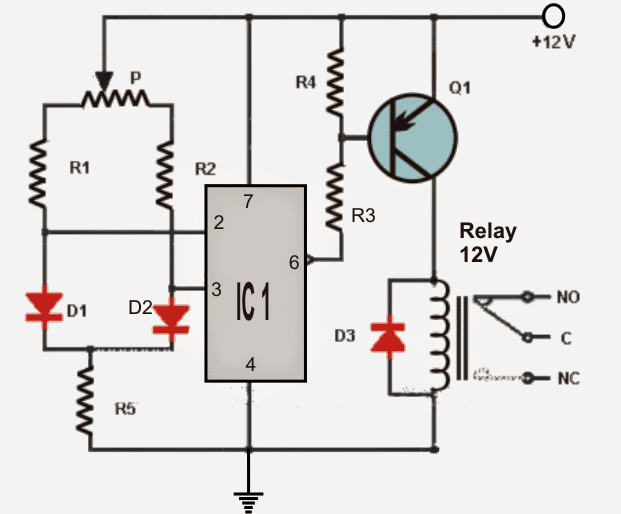

เฟสล็อกลูปประกอบด้วยเครื่องตรวจจับเฟส a ออสซิลเลเตอร์ควบคุมแรงดันไฟฟ้า และในระหว่างนั้นตัวกรองความถี่ต่ำได้รับการแก้ไข สัญญาณอินพุต 'Vi' ที่มีความถี่อินพุต 'Fi' ถูกควบคุมโดยเครื่องตรวจจับเฟส โดยทั่วไปเครื่องตรวจจับเฟสคือ เครื่องเปรียบเทียบ ที่เปรียบเทียบ fi ความถี่อินพุตผ่านความถี่ป้อนกลับสำหรับ เอาต์พุตของเครื่องตรวจจับเฟสคือ (fi + fo) ซึ่งเป็นแรงดันไฟฟ้ากระแสตรง เครื่องตรวจจับเฟสออกนั่นคือแรงดันไฟฟ้ากระแสตรงจะถูกป้อนไปยังตัวกรองความถี่ต่ำ (LPF) ซึ่งจะขจัดเสียงรบกวนความถี่สูงและสร้างระดับ DC ที่คงที่นั่นคือ Fi-Fo Vf ยังเป็นลักษณะไดนามิกของ PLL

แผนภาพบล็อก PLL

เอาต์พุตของตัวกรองความถี่ต่ำเช่นระดับ DC จะถูกส่งต่อไปยัง VCO สัญญาณอินพุตเป็นสัดส่วนโดยตรงกับความถี่เอาต์พุตของ VCO (สำหรับ) ความถี่อินพุตและเอาต์พุตจะถูกเปรียบเทียบและปรับผ่านลูปป้อนกลับจนกว่าความถี่เอาต์พุตจะเท่ากับความถี่อินพุต ดังนั้น PLL จึงทำงานเหมือนการทำงานฟรีการจับภาพและการล็อกเฟส

เมื่อไม่มีการใช้แรงดันไฟฟ้าขาเข้าจะกล่าวว่าเป็นขั้นตอนการวิ่งฟรี ทันทีที่ความถี่อินพุตที่ใช้กับ VOC เปลี่ยนแปลงและสร้างความถี่เอาต์พุตเพื่อเปรียบเทียบจะเรียกว่าสเตจจับภาพ รูปด้านล่างแสดงแผนภาพบล็อกของ PLL

Phase-Locked Loop Detector

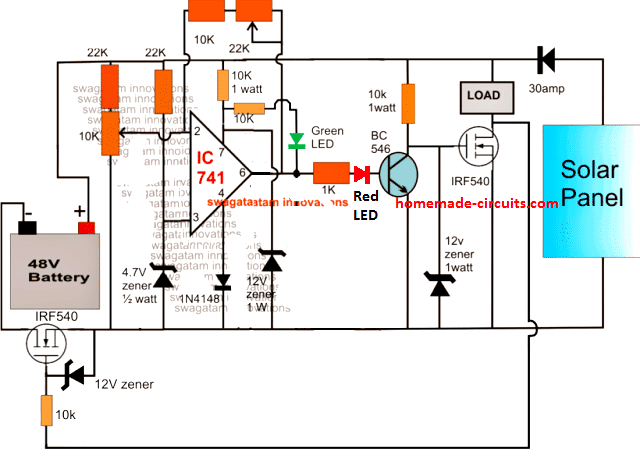

เครื่องตรวจจับลูปเฟสล็อกจะเปรียบเทียบความถี่อินพุตและความถี่เอาต์พุตของ VCO เพื่อสร้างแรงดันไฟฟ้ากระแสตรงซึ่งเป็นสัดส่วนโดยตรงกับความแตกต่างของเฟสของความถี่ทั้งสอง สัญญาณอนาล็อกและดิจิตอลถูกใช้ในเฟสล็อกลูป PLL เสาหินส่วนใหญ่ วงจรรวม ใช้เครื่องตรวจจับเฟสอะนาล็อกและเครื่องตรวจจับเฟสส่วนใหญ่มาจากประเภทดิจิตอล วงจรผสมสมดุลสองชั้นมักใช้ในเครื่องตรวจจับเฟสอะนาล็อก เครื่องตรวจจับเฟสทั่วไปบางตัวได้รับด้านล่าง:

เครื่องตรวจจับเฉพาะหรือเฟส

เครื่องตรวจจับเฟสหรือเฟสพิเศษคือชนิด CMOS IC 4070 ความถี่อินพุตและเอาต์พุตจะใช้กับตัวตรวจจับเฟส EX หรือเฟส เพื่อให้ได้เอาต์พุตสูงอย่างน้อยหนึ่งอินพุตควรต่ำและเงื่อนไขอื่น ๆ ของเอาต์พุตต่ำซึ่งแสดงไว้ในตารางความจริงด้านล่าง ให้เราพิจารณารูปคลื่นความถี่อินพุตและเอาต์พุตเช่น fi และ fo มีความแตกต่างของเฟส 0 องศา จากนั้นแรงดันเอาต์พุต DC ของเครื่องเปรียบเทียบจะเป็นฟังก์ชันของความแตกต่างของเฟสระหว่างอินพุตทั้งสอง

| เป็น | สำหรับ | Vdc |

ต่ำ | ต่ำ | ต่ำ |

ต่ำ | สูง | สูง |

สูง | ต่ำ | สูง |

สูง | สูง | ต่ำ |

ฟังก์ชั่นของความแตกต่างเฟสระหว่าง fi และ fo ดังแสดงในกราฟของแรงดันไฟฟ้าขาออก DC หากเครื่องตรวจจับเฟสอยู่ที่ 180 องศาแสดงว่าแรงดันเอาต์พุตสูงสุด หากทั้งความถี่อินพุตและเอาต์พุตเป็นคลื่นสี่เหลี่ยมจะใช้เครื่องตรวจจับเฟสประเภทนี้

เครื่องตรวจจับเฉพาะหรือเฟส

Edge Trigger Phase Detector

เครื่องตรวจจับเฟสทริกเกอร์ขอบใช้เมื่อความถี่อินพุตและเอาต์พุตอยู่ในรูปคลื่นพัลส์ซึ่งน้อยกว่ารอบการทำงาน 50% ฟลิปฟล็อป R-S ใช้สำหรับเครื่องตรวจจับเฟสซึ่งแสดงในรูปด้านล่าง ถึงจาก R-S รองเท้าแตะ ประตู NOR ทั้งสองเป็นแบบไขว้กัน เอาต์พุตของเครื่องตรวจจับเฟสสามารถเปลี่ยนสถานะลอจิกได้โดยการเรียกใช้ฟลิปฟล็อป R-S ขอบบวกของความถี่อินพุตและเอาต์พุตสามารถเปลี่ยนเอาต์พุตของตัวตรวจจับเฟสได้

Edge Trigger Phase Detector

เครื่องตรวจจับเฟสเสาหิน

เครื่องตรวจจับเฟสเสาหินเป็นประเภท CMOS เช่น IC 4044 ซึ่งได้รับการชดเชยอย่างมากจากความไวฮาร์มอนิกและปัญหาของวงจรการทำงานจะถูกละทิ้งเนื่องจากวงจรสามารถตอบสนองต่อการเปลี่ยนสัญญาณอินพุตเท่านั้น ในการใช้งานที่สำคัญมันเป็นเครื่องตรวจจับเฟสที่มีไข้มากที่สุด ความแตกต่างที่เป็นอิสระของแอมพลิจูดนั้นปราศจากข้อผิดพลาดของเฟสแรงดันไฟฟ้าผิดพลาดของเอาต์พุตและวัฏจักรหน้าที่ของรูปคลื่นอินพุต

การประยุกต์ใช้ Phase-Locked Loop

- เครือข่ายการถอดรหัส FM สำหรับการทำงานของ FM

- มันถูกใช้ใน การควบคุมความเร็วมอเตอร์ และตัวกรองการติดตาม

- ใช้ในการถอดรหัสการเปลี่ยนความถี่สำหรับความถี่ของพาหะดีมอดูเลต

- มันถูกใช้ในเวลาเป็นตัวแปลงดิจิทัล

- ใช้สำหรับการลดกระวนกระวายใจการลดความเบ้การกู้คืนนาฬิกา

ทั้งหมดนี้เกี่ยวกับหลักการทำงานและการดำเนินงานของเฟสล็อกลูปและการใช้งาน เราหวังว่าข้อมูลที่ให้ไว้ในบทความนี้จะเป็นประโยชน์ต่อคุณในการทราบข้อมูลบางอย่างเกี่ยวกับโครงการและทำความเข้าใจกับมัน นอกจากนี้หากคุณมีข้อสงสัยเกี่ยวกับบทความนี้และใน โครงการไฟฟ้าและอิเล็กทรอนิกส์ คุณสามารถแสดงความคิดเห็นได้ในส่วนด้านล่าง นี่คือคำถามสำหรับคุณวิธีที่ดีที่สุดในการจำลอง PLL เพื่อความเสถียรคืออะไร?

เครดิตภาพ:

- แผนภาพบล็อกของ PLL วงจร

- เครื่องตรวจจับเฉพาะหรือเฟส สถานที่ศักดิ์สิทธิ์

- Edge Trigger Phase Detector เรียนรู้เกี่ยวกับอิเล็กทรอนิกส์