โดยทั่วไปตัวลบเต็มเป็นหนึ่งในตัวลบที่ใช้มากที่สุดและ วงจรลอจิกเชิงผสมที่จำเป็น . เป็นอุปกรณ์อิเล็กทรอนิกส์พื้นฐานที่ใช้ในการลบเลขฐานสองสองตัว ในบทความก่อนหน้านี้เราได้ให้ทฤษฎีพื้นฐานของ แอดเดอร์ครึ่งตัวและแอดเดอร์เต็ม ซึ่งใช้เลขฐานสองสำหรับการคำนวณ ในทำนองเดียวกันตัวลบเต็มจะใช้เลขฐานสองเช่น 0,1 สำหรับการลบ วงจรนี้สามารถสร้างด้วยลอจิกเกตเช่น OR, Ex-OR, NAND gate อินพุตของตัวลบนี้คือ A, B, Bin และเอาต์พุตคือ D, Bout

บทความนี้ให้แนวคิดทฤษฎีตัวลบเต็มรูปแบบซึ่งประกอบด้วยสถานที่ต่างๆเช่นตัวลบคืออะไรการออกแบบด้วยลอจิกเกตตารางความจริง ฯลฯ บทความนี้มีประโยชน์สำหรับนักศึกษาวิศวกรรมที่สามารถอ่านหัวข้อเหล่านี้ได้ในห้องปฏิบัติการ HDL Practical

Subtractor คืออะไร?

การลบเลขฐานสองสามารถทำได้ด้วยความช่วยเหลือของวงจรลบ นี่คือวงจรลอจิกเชิงผสมชนิดหนึ่งที่ใช้ในการลบเลขฐานสองสองหลักเช่น 0s และ 1s การลบเลขฐานสองจาก 0 ถึง 0 หรือ 0 ถึง 1 จะไม่เปลี่ยนผลลัพธ์การลบ 1 ถึง 1 จะให้ผลลัพธ์เป็น 0 แต่การลบ 1 ถึง 0 จำเป็นต้องยืม

ตัวอย่างเช่นวงจรลบสองบิตประกอบด้วยอินพุตสองตัวเช่น A & B ในขณะที่เอาต์พุตเป็นความแตกต่างและยืม วงจรนี้สามารถสร้างขึ้นโดยใช้แอดเดอร์พร้อมกับอินเวอร์เตอร์ซึ่งตั้งอยู่ท่ามกลางอินพุตข้อมูลทั้งหมดรวมทั้งอินพุตยืม (Bin) ของเฟสก่อนหน้าของ FA

ตัวลบแบ่งออกเป็นสองประเภทเช่นตัวลบครึ่งตัวและตัวลบเต็ม ที่นี่เรากำลังพูดถึงตัวลบเต็ม

Full Subtractor คืออะไร?

เป็นอุปกรณ์อิเล็กทรอนิกส์หรือ วงจรลอจิก ซึ่งทำการลบเลขฐานสองสองหลัก เป็นวงจรลอจิกเชิงผสมที่ใช้ในอุปกรณ์อิเล็กทรอนิกส์ดิจิทัล มีวงจรรวมอยู่ใน เทคโนโลยีวงจรรวม ได้แก่ แอดเดอร์ตัวเข้ารหัสตัวถอดรหัสและมัลติเพล็กเซอร์ ในบทความนี้เราจะพูดถึงการสร้างโดยใช้ตัวลบครึ่งหนึ่งและคำศัพท์เช่นตารางความจริง

ตัวลบเต็ม

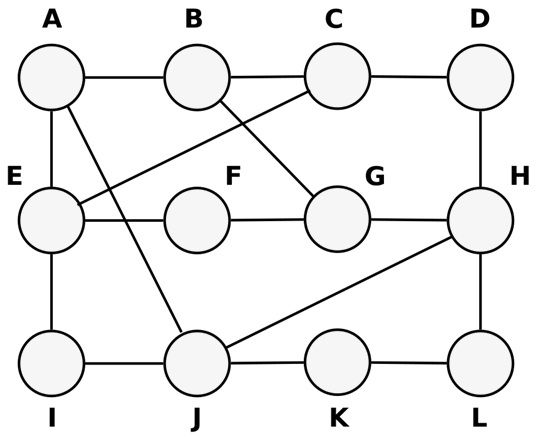

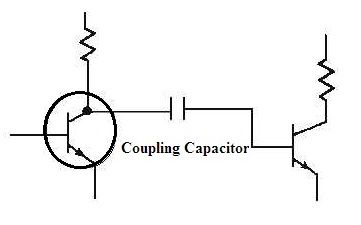

การออกแบบสิ่งนี้สามารถทำได้โดยตัวลบครึ่งตัวสองตัวซึ่งเกี่ยวข้องกับอินพุตสามตัวเช่น minuend ลบและยืมบิตยืมระหว่างอินพุตได้มาจากการลบเลขฐานสองสองหลักและลบออกจากคู่ลำดับที่สูงกว่าถัดไปของ บิตผลลัพธ์เป็นความแตกต่างและยืม

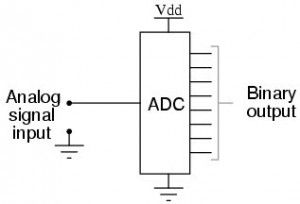

แผนภาพบล็อกตัวลบแบบเต็ม ดังแสดงด้านล่าง ข้อเสียที่สำคัญที่สุดของตัวลบครึ่งหนึ่งคือเราไม่สามารถทำการยืมบิตในตัวลบนี้ได้ ในการออกแบบจริงๆแล้วเราสามารถสร้างบิต Borrow ในวงจรและสามารถลบด้วย i / ps ที่เหลืออีกสองตัว ที่นี่ A คือ minuend, B คือ subtrahend & Bin คือยืมมาผลลัพธ์คือ Difference (ความแตกต่าง) & Bout (ยืมออก) วงจรลบที่สมบูรณ์สามารถรับได้โดยใช้ตัวลบครึ่งตัวสองตัวพร้อมประตูพิเศษหรือ

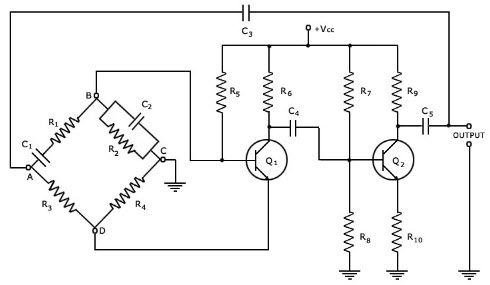

แผนภาพวงจรลบแบบเต็มพร้อมลอจิกเกตส์

แผนภาพวงจรของตัวลบเต็มโดยใช้ประตูพื้นฐาน s แสดงในแผนภาพบล็อกต่อไปนี้ วงจรนี้สามารถทำได้ด้วยวงจร half-Subtractor สองวงจร

ในวงจร half-Subtractor เริ่มต้นอินพุตไบนารีคือ A และ B ตามที่เราได้กล่าวไปแล้วในบทความ half-Subtractor ก่อนหน้านี้จะสร้างเอาต์พุตสองเอาต์พุตคือความแตกต่าง (Diff) และการยืม

ตัวลบแบบเต็มโดยใช้ Logic Gates

ความแตกต่าง o / p ของตัวลบด้านซ้ายมอบให้กับวงจรครึ่งตัวลบด้านซ้าย เอาต์พุตที่แตกต่างจะถูกจัดเตรียมไว้ให้กับอินพุตของวงจร Subtractor ครึ่งขวา เราเสนอการยืมเป็นบิตใน i / p อื่น ๆ ของถัดไป วงจรลบครึ่งหนึ่ง . อีกครั้งจะมีการแจก Diff และ Borrow out ผลลัพธ์สุดท้ายของตัวลบนี้คือ Diff-output

ในทางกลับกันการยืมออกจากวงจร Subtractor ทั้งสองแบบเชื่อมต่อกับหรือลอจิกเกต หลังจากการแจกแจง OR ลอจิกสำหรับสองบิตเอาต์พุตของตัวลบเราจะได้รับ Borrow สุดท้ายจากตัวลบ การยืมครั้งสุดท้ายเพื่อแสดงถึง MSB (บิตที่สำคัญที่สุด)

ถ้าเราสังเกตวงจรภายในของสิ่งนี้เราจะเห็น Half Subtractors สองตัวพร้อมประตู NAND และประตู XOR พร้อมประตูพิเศษหรือ

ตารางความจริงตัวลบแบบเต็ม

นี้ วงจรลบ ดำเนินการลบระหว่างสองบิตซึ่งมี 3- อินพุต (A, B และ Bin) และสองเอาต์พุต (D และ Bout) ที่นี่ปัจจัยการผลิตจะระบุ minuend, subtrahend และการยืมก่อนหน้าในขณะที่เอาต์พุตทั้งสองแสดงว่าเป็นยืม o / p และผลต่าง ภาพต่อไปนี้แสดงตารางความจริงของตัวลบเต็ม

อินพุต | เอาท์พุต | |||

นาที (A) | ลบ (B) | ยืม (Bin) | ความแตกต่าง (D) | ยืม (แข่งขัน) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

K- แผนที่

ความเรียบง่ายของไฟล์ ตัวลบเต็ม K-map สำหรับความแตกต่างข้างต้นและการยืมแสดงอยู่ด้านล่าง

สมการสำหรับความแตกต่างเช่นเดียวกับ Bin จะกล่าวถึงด้านล่าง

นิพจน์สำหรับความแตกต่างคือ

D = A’B’Bin + AB’Bin ’+ A’BBin’ + ABBin

นิพจน์สำหรับ Borrow คือ

Bout = A’Bin + A’B + BBin

การเรียงซ้อนของวงจรตัวลบแบบเต็ม

ก่อนหน้านี้เราได้พูดถึงภาพรวมของสิ่งนี้เช่นการก่อสร้างแผนภาพวงจรพร้อมลอจิกเกต แต่ถ้าเราต้องการลบตัวเลข 1 บิตสองตัวออกไปวงจรการลบนี้มีประโยชน์มากในการเรียงซ้อนตัวเลขบิตเดียวและลบเลขฐานสองมากกว่าสองตัว ในกรณีเช่นนี้จะใช้วงจรเรียงซ้อน adder แบบเต็มโดยใช้ NOT logic gate การแปลงวงจรจากแอดเดอร์เต็มเป็นตัวลบเต็มสามารถทำได้โดยใช้เทคนิคเสริม 2

โดยทั่วไปให้กลับอินพุตลบสำหรับแอดเดอร์เต็มโดยใช้ NOT gate มิฉะนั้นอินเวอร์เตอร์ ด้วยการเพิ่ม Minuend (อินพุตที่ไม่กลับด้าน) & Subtrahend (Inverted Input) LSB (นำอินพุต) ของวงจร FA คือ 1 ซึ่งหมายความว่า Logic High มิฉะนั้นเราจะลบเลขฐานสองสองหลักโดยใช้เทคนิคการเติมเต็ม 2 ผลลัพธ์ของ FA คือบิตที่แตกต่างกันและหากเราสลับการดำเนินการเราจะได้รับ MSB เป็นอย่างอื่น Borrow bit จริงๆแล้วเราสามารถออกแบบวงจรเพื่อให้สังเกตเห็นเอาต์พุตได้

รหัส Verilog

สำหรับส่วนการเข้ารหัสอันดับแรกเราต้องตรวจสอบโครงสร้างของการสร้างแบบจำลองของแผนภาพวงจรลอจิก แผนภาพลอจิกของสิ่งนี้สามารถสร้างได้โดยใช้เกต AND, วงจรลบครึ่งหนึ่งและการรวมกันของลอจิกเกตเช่น AND, OR, NOT, XOR เกต ในการสร้างแบบจำลองโครงสร้างเราจะอธิบายโมดูลต่างๆสำหรับการจัดเรียงองค์ประกอบพื้นฐานทั้งหมด ในโค้ดต่อไปนี้สามารถกำหนดโมดูลที่แตกต่างกันสำหรับทุกเกต

โมดูลนี้มีไว้สำหรับประตู OR

อินพุต: a0, b0

เอาท์พุท: c0

สุดท้ายนี้เราจะรวมโมดูลที่แม่นยำของประตูเหล่านี้ไว้ในโมดูลเดียว สำหรับสิ่งนั้นที่นี่เราใช้การสร้างอินสแตนซ์ของโมดูล ตอนนี้อินสแตนซ์นี้สามารถใช้ได้เมื่อเราต้องการจำลองโมดูลหรือฟังก์ชันที่แน่นอนสำหรับชุดอินพุตที่หลากหลาย ขั้นแรกเราออกแบบตัวลบครึ่งหนึ่งจากนั้นโมดูลนี้จะใช้เพื่อใช้ตัวลบแบบเต็ม สำหรับการดำเนินการนี้เราใช้ประตู OR เพื่อรวม o / ps สำหรับตัวแปรของ Bout รหัส verilog สำหรับตัวลบเต็ม ดังแสดงด้านล่าง

โมดูล or_gate (a0, b0, c0)

ป้อน a0, b0

เอาต์พุต c0

กำหนด c0 = a0 | b0

endmodule

โมดูล xor_gate (a1, b1, c1)

ป้อน a1, b1

เอาต์พุต c1

กำหนด c1 = a1 ^ b1

endmodule

โมดูล and_gate (a2, b2, c2)

ป้อน a2, b2

เอาต์พุต c2

กำหนด c2 = a2 & b2

endmodule

โมดูล not_gate (a3, b3)

ป้อน a3

เอาต์พุต b3

กำหนด b3 = ~ a3

endmodule

โมดูล half_subtractor (a4, b4, c4, d4)

ป้อน a4, b4

เอาต์พุต c4, d4

ลวด x

xor_gate u1 (a4, b4, c4)

and_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

endmodule

โมดูล full_subtractor (A, B, Bin, D, Bout)

อินพุต A, B, Bin

เอาต์พุต D, Bout

ลวด p, q, r

half_subtractor u4 (A, B, p, q)

half_subtractor u5 (p, Bin, D, r)

or_gate u6 (q, r, Bout)

endmodule

ตัวลบแบบเต็มโดยใช้ 4X1 Multiplexer

การดำเนินการลบสามารถทำได้โดยใช้วิธีการเสริมทั้งสอง ดังนั้นเราจึงต้องใช้เกต 1-XOR ซึ่งใช้ในการแปลง 1 บิตและรวมเข้าไว้ในบิตพกพา เอาต์พุตของ DIFFERENCE นั้นคล้ายกับเอาต์พุต SUM ในวงจรแอดเดอร์เต็ม แต่ BARROW o / p ไม่เหมือนกับเอาต์พุตพกพาของแอดเดอร์เต็ม แต่จะกลับด้านเช่นเดียวกับคำชมเช่น A - B = A + (-B) = A + สองส่วนเติมเต็มของ B

การออกแบบโดยใช้มัลติเพล็กเซอร์ 4X1 แสดงในแผนภาพตรรกะต่อไปนี้ การออกแบบนี้สามารถทำได้โดยใช้ขั้นตอนต่อไปนี้

4X1 มัลติเพล็กเซอร์

- ในขั้นตอนที่ 1 มีสองเอาต์พุตเช่น Sub และ Borrow เราจึงต้องเลือกมัลติเพล็กเซอร์ 2 ตัว

- ในขั้นตอนที่ 2 สามารถใช้ตารางความจริงร่วมกับ K-maps ได้

- ในขั้นตอนที่ 3 คุณสามารถเลือกตัวแปรทั้งสองเป็นบรรทัดเลือกของคุณได้ ตัวอย่างเช่น B & C อยู่ในกรณีนี้

ตารางความจริง

ตารางความจริงของตัวลบเต็ม วงจรที่ใช้มัลติเพล็กเซอร์ 4X1 มีดังต่อไปนี้

ถึง | ข | ค | ย่อย | ยืม |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

ตัวลบแบบเต็มโดยใช้ตัวถอดรหัส

การออกแบบตัวลบแบบเต็มโดยใช้ตัวถอดรหัส 3-8 ตัวสามารถทำได้โดยใช้เอาต์พุตต่ำที่ใช้งานอยู่ สมมติว่าตัวถอดรหัสทำงานโดยใช้แผนภาพตรรกะต่อไปนี้ ตัวถอดรหัสประกอบด้วยอินพุตสามตัวในตัวถอดรหัส 3-8 ตัว จากตารางความจริงเราสามารถเขียน minterms สำหรับผลลัพธ์ของความแตกต่างและยืม

จากตารางความจริงข้างต้น

สำหรับฟังก์ชันต่างๆในตารางความจริง minterms สามารถเขียนได้เป็น 1,2,4,7 และในทำนองเดียวกันสำหรับการยืม minterms สามารถเขียนได้เป็น 1,2,3,7 ตัวถอดรหัส 3-8 ประกอบด้วยอินพุตสามตัวและเอาต์พุต 8 ตัว lik0 ถึง 7 ตัวเลข

ตัวถอดรหัส 3 ถึง 8

หากอินพุตของตัวลบคือ 000 เอาต์พุต '0' จะทำงานและหากอินพุตเป็น 001 เอาต์พุต '1' จะทำงาน

ตอนนี้เอาต์พุตของตัวลบสามารถนำมาจาก 1, 2, 4 และ 7 เพื่อเชื่อมต่อกับประตู NAND จากนั้นเอาต์พุตจะเป็นผลต่าง เอาต์พุตเหล่านี้สามารถเชื่อมต่อกับลอจิกเกต NAND อื่น ๆ โดยที่เอาต์พุตเปลี่ยนเป็นการยืม

ตัวอย่างเช่นหากอินพุตเป็น 001 เอาต์พุตจะเป็น 1 ซึ่งหมายความว่ามีการใช้งานอยู่ ดังนั้นเอาต์พุตจึงแอ็คทีฟต่ำและสามารถรับเอาต์พุตได้จากประตู NAND เรียกว่าฟังก์ชันความแตกต่างเช่นฟังก์ชันสูงและฟังก์ชันยืมก็เปลี่ยนเป็นสูงเช่นกัน ดังนั้นเราจึงได้ผลลัพธ์ที่ต้องการ ในที่สุดตัวถอดรหัสจะทำงานเหมือนตัวลบเต็มรูปแบบ

ข้อดีและข้อเสีย

ข้อดีของตัวลบ รวมสิ่งต่อไปนี้

- การออกแบบตัวลบนั้นง่ายมากเช่นเดียวกับการใช้งาน

- การหักกำลังภายใน DSP (การประมวลผลสัญญาณดิจิตอล)

- งานด้านการคำนวณสามารถทำได้ด้วยความเร็วสูง

ข้อเสียของตัวลบ รวมสิ่งต่อไปนี้

- ในตัวลบครึ่งหนึ่งไม่มีเงื่อนไขใดที่จะยอมรับอินพุตแบบยืมจากเฟสก่อนหน้านี้

- ความเร็วของตัวลบสามารถเป็นบางส่วนผ่านความล่าช้าในวงจร

การใช้งาน

บางส่วนของ แอพพลิเคชั่นของตัวลบเต็ม รวมสิ่งต่อไปนี้

- โดยทั่วไปจะใช้สำหรับ ALU (Arithmetic logic unit) ในคอมพิวเตอร์เพื่อลบเป็น CPU และ GPU สำหรับการใช้งานกราฟิกเพื่อลดความยากของวงจร

- ตัวลบส่วนใหญ่จะใช้ในการทำฟังก์ชันทางคณิตศาสตร์เช่นการลบในเครื่องคิดเลขอิเล็กทรอนิกส์และอุปกรณ์ดิจิทัล

- นอกจากนี้ยังสามารถใช้ได้กับ ไมโครคอนโทรลเลอร์ที่แตกต่างกัน สำหรับการลบเลขคณิตตัวจับเวลาและตัวนับโปรแกรม (PC)

- ตัวลบถูกใช้ในโปรเซสเซอร์เพื่อคำนวณตารางที่อยู่ ฯลฯ

- นอกจากนี้ยังมีประโยชน์สำหรับ DSP และระบบเครือข่าย

- สิ่งเหล่านี้ใช้เป็นหลักสำหรับ ALU ภายในคอมพิวเตอร์สำหรับการลบเช่น CPU & GPU สำหรับแอพพลิเคชั่นกราฟิกเพื่อลดความซับซ้อนของวงจร

- สิ่งเหล่านี้ส่วนใหญ่จะใช้เพื่อทำหน้าที่ทางคณิตศาสตร์เช่นการลบภายในอุปกรณ์ดิจิทัลเครื่องคิดเลขเป็นต้น

- ตัวลบเหล่านี้ยังเหมาะสำหรับไมโครคอนโทรลเลอร์ต่างๆสำหรับตัวจับเวลาพีซี (ตัวนับโปรแกรม) และการลบเลขคณิต

- สิ่งเหล่านี้ใช้สำหรับโปรเซสเซอร์ในการคำนวณที่อยู่ตาราง ฯลฯ

- การนำสิ่งนี้ไปใช้กับลอจิกเกตเช่น NAND & NOR สามารถทำได้ด้วยวงจรลอจิกลบแบบเต็มเนื่องจากทั้งประตู NOR และ NAND เรียกว่าประตูสากล

จากข้อมูลข้างต้นโดยการประเมิน adder ตัวลบเต็มโดยใช้วงจรลบครึ่งตัวสองตัวและรูปแบบตารางเราสามารถสังเกตได้ว่า Dout ใน full-subtractor นั้นคล้ายกับ Sout ของ full-adder รูปแบบเดียวคือ A (ตัวแปรอินพุต) ถูกเติมเต็มในตัวลบเต็ม ดังนั้นจึงเป็นไปได้ที่จะเปลี่ยนวงจร full-adder ให้เป็น full-subtractor โดยเพียงเติม i / p A ก่อนที่จะกำหนดให้ ประตูตรรกะ เพื่อสร้างเอาต์พุตการยืมบิตสุดท้าย (Bout)

ด้วยการใช้วงจรลอจิกลบแบบเต็มจะทำให้ตัวลบเต็มโดยใช้ประตู NAND และตัวลบเต็มโดยใช้หรือประตูไม่สามารถใช้งานได้เนื่องจากทั้งประตู NAND และ NOR จะถือว่าเป็นประตูสากล นี่คือคำถามสำหรับคุณความแตกต่างระหว่างตัวลบครึ่งตัวและตัวลบเต็มคืออะไร?