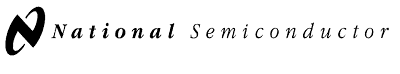

ในโดเมนของอุปกรณ์อิเล็กทรอนิกส์แนวคิดที่สำคัญที่สุดที่ทุกองค์ประกอบใช้งานได้คือ“ ลอจิกเกตส์ “. เนื่องจากแนวคิดของลอจิกเกตถูกนำไปใช้ในทุกฟังก์ชันการทำงานเช่นในวงจรรวมเซ็นเซอร์วัตถุประสงค์ในการเปลี่ยนไมโครคอนโทรลเลอร์และโปรเซสเซอร์วัตถุประสงค์ในการเข้ารหัสและถอดรหัสและอื่น ๆ นอกจากนี้ยังมีแอพพลิเคชั่น Logic Gates มากมาย ลอจิกเกตมีหลายประเภทเช่น Adder, Subtractor, Full แอดเดอร์ , Full Subtractor, Half Subtractor และอื่น ๆ อีกมากมาย ดังนั้นบทความนี้จึงให้ข้อมูลโดยรวมของ วงจรลบครึ่งหนึ่ง , ตารางความจริงตัวลบครึ่งหนึ่ง และแนวคิดที่เกี่ยวข้อง

Half Subtractor คืออะไร?

ก่อนที่จะพูดถึงการลบครึ่งหนึ่งเราต้องรู้จักการลบเลขฐานสอง ในการลบเลขฐานสองกระบวนการลบจะคล้ายกับการลบเลขคณิต ในการลบเลขคณิตจะใช้ระบบเลขฐาน 2 ในขณะที่การลบเลขฐานสองจะใช้เลขฐานสองสำหรับการลบ เงื่อนไขผลลัพธ์สามารถแสดงด้วยความแตกต่างและยืม

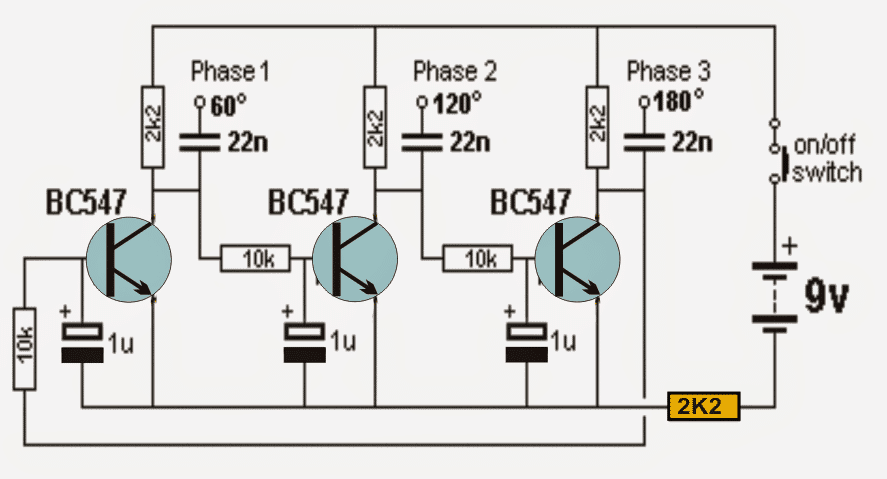

ตัวลบครึ่งหนึ่งมีความสำคัญที่สุด วงจรลอจิกเชิงผสม ซึ่งใช้ใน อิเล็กทรอนิกส์ดิจิทัล . โดยพื้นฐานแล้วนี่คืออุปกรณ์อิเล็กทรอนิกส์หรืออีกนัยหนึ่งเราสามารถพูดได้ว่าเป็นวงจรลอจิก วงจรนี้ใช้ในการลบเลขฐานสองสองหลัก ในบทความก่อนหน้านี้เราได้กล่าวไปแล้ว แนวคิดของ half adder และวงจร adder เต็มรูปแบบ ซึ่งใช้เลขฐานสองในการคำนวณ ในทำนองเดียวกันวงจรลบจะใช้เลขฐานสอง (0,1) สำหรับการลบ วงจรของตัวลบครึ่งหนึ่งสามารถสร้างได้ด้วยสองตัว ลอจิกเกตคือ NAND และ EX-OR ประตู . วงจรนี้ให้สององค์ประกอบเช่นความแตกต่างเช่นเดียวกับที่พวกเขายืม

เช่นเดียวกับการลบเลขฐานสองเลขหลักคือ 1 เราสามารถสร้างการยืมได้ในขณะที่การลบ 1 นั้นดีกว่าค่าลบ 0 และด้วยเหตุนี้การยืมจึงจำเป็น ตัวอย่างต่อไปนี้ให้การลบไบนารีของสองบิตไบนารี

ตัวเลขแรก | ตัวเลขที่สอง | ความแตกต่าง | ยืม |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

ในการลบข้างต้นตัวเลขสองหลักสามารถแทนด้วย A และ B ได้ทั้งสองหลักนี้สามารถลบออกได้และให้บิตที่เป็นผลลัพธ์เป็นผลต่างและยืม

เมื่อเราสังเกตแถวสองและสี่แรกความแตกต่างระหว่างแถวเหล่านี้ความแตกต่างและการยืมจะใกล้เคียงกันเนื่องจากการลบมีค่าน้อยกว่าค่าต่ำสุด ในทำนองเดียวกันเมื่อเราสังเกตแถวที่สามค่าต่ำสุดจะถูกลบออกจากการลบ ดังนั้นความแตกต่างและบิตยืมจึงเป็น 1 เนื่องจากเลขที่ลบนั้นดีกว่าหลักต่ำสุด

วงจรผสมนี้เป็นเครื่องมือที่จำเป็นสำหรับทุกประเภท วงจรดิจิตอล เพื่อทราบการรวมกันของอินพุตและเอาต์พุตที่เป็นไปได้ ตัวอย่างเช่นหากตัวลบมีสองอินพุตผลลัพธ์ผลลัพธ์จะเป็นสี่ o / p ของตัวลบครึ่งหนึ่งถูกกล่าวถึงในตารางด้านล่างซึ่งจะหมายถึงบิตความแตกต่างและบิตยืม คำอธิบายตารางความจริงของวงจรสามารถทำได้โดยใช้ลอจิกเกตเช่น EX-OR ลอจิกเกตและการทำงานของเกตตามด้วย NOT gate

การแก้ตารางความจริงโดยใช้ K- แผนที่ ดังแสดงด้านล่าง

แผนที่ตัวลบครึ่งหนึ่ง k

นิพจน์ตัวลบครึ่งหนึ่ง การใช้ตารางความจริงและ K-map สามารถหาได้จาก

ความแตกต่าง (D) = ( x’y + xy ')

= x ⊕ y

ยืม (B) = x’y

วงจรลอจิก

วงจรลอจิกลบครึ่งหนึ่ง สามารถอธิบายได้โดยใช้ลอจิกเกต:

- 1 ประตู XOR

- 1 ไม่ใช่ประตู

- ประตู 1 AND

การเป็นตัวแทนคือ

วงจรลอจิกลบครึ่งหนึ่ง

Half-Subtractor Block Diagram

แผนภาพบล็อกของตัวลบครึ่งหนึ่งแสดงไว้ด้านบน มันต้องใช้สองอินพุตและให้สองเอาต์พุต อินพุตที่นี่แสดงด้วย A&B และเอาต์พุตคือความแตกต่างและการยืม

วงจรข้างต้นสามารถออกแบบได้ด้วยประตู EX-OR & NAND ที่นี่ประตู NAND สามารถสร้างได้โดยใช้และไม่ใช่ประตู ดังนั้นเราจึงต้องการลอจิกเกตสามตัวในการสร้างครึ่งวงจรลบคือ EX-OR เกตไม่ใช่เกตและเกต NAND

การรวมกันของประตู AND และ NOT ทำให้เกิดประตูรวมที่แตกต่างกันชื่อ NAND Gate เอาต์พุต Ex-OR gate จะเป็นบิตความแตกต่างและเอาต์พุต NAND Gate จะเป็นบิต Borrow สำหรับอินพุต A&B เดียวกัน

และประตู

AND-gate เป็นประตูลอจิกดิจิทัลประเภทหนึ่งที่มีอินพุตหลายตัวและเอาต์พุตเดียวและขึ้นอยู่กับการรวมกันของอินพุตซึ่งจะทำการเชื่อมต่อแบบลอจิคัล เมื่ออินพุตทั้งหมดของเกตนี้สูงเอาต์พุตจะสูงมิฉะนั้นเอาต์พุตจะต่ำ แผนภาพลอจิกของ AND gate with truth table แสดงไว้ด้านล่าง

และประตูและตารางความจริง

ไม่ใช่ประตู

NOT-gate เป็นประตูลอจิกดิจิทัลประเภทหนึ่งที่มีอินพุตเดียวและขึ้นอยู่กับอินพุตเอาต์พุตจะถูกย้อนกลับ ตัวอย่างเช่นเมื่ออินพุตของประตู NOT สูงเอาต์พุตจะต่ำ แผนภาพลอจิกของ NOT-gate พร้อมตารางความจริงแสดงไว้ด้านล่าง ด้วยการใช้ลอจิกเกตประเภทนี้เราสามารถเรียกใช้ NAND และ NOR เกตได้

ไม่ใช่ประตูและตารางความจริง

ประตู Ex-OR

Exclusive-OR หรือ EX-OR gate คือ digital logic gate ประเภทหนึ่งที่มี 2-inputs & single output การทำงานของลอจิกเกตนี้ขึ้นอยู่กับประตูหรือ หากอินพุตของเกตนี้มีค่าสูงเอาต์พุตของเกต EX-OR ก็จะสูง ตารางสัญลักษณ์และความจริงของ EX-OR แสดงอยู่ด้านล่าง

ประตู XOR และตารางความจริง

Half Subtractor Circuit โดยใช้ Nand Gate

การออกแบบตัวลบสามารถทำได้โดย ใช้ลอจิกเกต เช่นประตู NAND และประตู Ex-OR ในการออกแบบวงจรลบครึ่งตัวนี้เราต้องรู้สองแนวคิดคือความแตกต่างและการยืม

Half Subtractor Circuit โดยใช้ Nand Gate

หากเราตรวจสอบอย่างระมัดระวังจะค่อนข้างชัดเจนว่าความหลากหลายของการทำงานที่ดำเนินการโดยวงจรนี้ซึ่งเกี่ยวข้องอย่างถูกต้องกับการทำงานของ EX-OR gate ดังนั้นเราสามารถใช้ประตู EX-OR เพื่อสร้างความแตกต่างได้ ในทำนองเดียวกันการยืมที่ผลิตโดยวงจรแอดเดอร์ครึ่งหนึ่งสามารถทำได้โดยใช้การผสมผสานของลอจิกเกตเช่น AND- เกตและ NOT-gate

HS นี้สามารถออกแบบได้โดยใช้ประตู NOR ซึ่งต้องใช้ประตู 5 NOR ในการก่อสร้าง แผนภาพวงจรลบครึ่งตัวโดยใช้ประตู NOR แสดงเป็น:

ตัวลบครึ่งหนึ่งโดยใช้ Nor Gates

ตารางความจริง

บิตแรก | บิตที่สอง | ความแตกต่าง (อดีตหรือออก) | ยืม (NAND ออก) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

VHDL และ Testbench Code

รหัส VHDL สำหรับตัวลบครึ่งหนึ่งอธิบายได้ดังนี้:

ไลบรารี IEEE

ใช้ IEEE.STD_LOGIC_1164.ALL

ใช้ IEEE.STD_LOGIC_ARITH.ALL

ใช้ IEEE.STD_LOGIC_UNSIGNED.ALL

เอนทิตี Half_Sub1 คือ

พอร์ต (a: ใน STD_LOGIC

b: ใน STD_LOGIC

HS_Diff: ออก STD_LOGIC

HS_Borrow: ออก STD_LOGIC)

จบ Half_Sub1

สถาปัตยกรรม Behavioral ของ Half_Sub1 คือ

เริ่ม

HS_Diff<=a xor b

HS_Borrow<=(not a) and b

รหัส testbench สำหรับ HS อธิบายได้ดังนี้:

ห้องสมุด IEEE

ใช้ ieee.std_logic_1164.ALL

ENTITY HS_tb IS

END HS_tb

ARCHITECTURE HS_tb ของ HS_tb IS

ส่วนประกอบ HS

PORT (a: ใน std_logic

b: ใน std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

จบส่วนประกอบ

ส่งสัญญาณ a: std_logic: = ‘0’

สัญญาณ b: std_logic: = ‘0’

สัญญาณ HS_Diff: std_logic

สัญญาณ HS_Borrow: std_logic

เริ่ม

ใหม่: แผนที่พอร์ต HS (

ก => ก,

b => ข,

HS_Diff => HS_Diff,

HS_borrow => HS_borrow

)

stim_proc: กระบวนการ

เริ่ม

ถึง<= ‘0’

ข<= ‘0’

รอ 30 ns

ถึง<= ‘0’

ข<= ‘1’

รอ 30 ns

ถึง<= ‘1’

ข<= ‘0’

รอ 30 ns

ถึง<= ‘1’

ข<= ‘1’

รอ

สิ้นสุดกระบวนการ

สิ้นสุด

ตัวลบเต็มโดยใช้ตัวลบครึ่งหนึ่ง

ตัวลบเต็มเป็นอุปกรณ์ผสมที่ดำเนินการฟังก์ชันการลบโดยใช้สองบิตและเป็น minuend และ subtrahend วงจรจะพิจารณายืมเอาต์พุตก่อนหน้านี้และมีอินพุตสามตัวพร้อมเอาต์พุตสองตัว อินพุตสามอินพุตคือ minuend, subtrahend และอินพุตที่ได้รับจากเอาต์พุตก่อนหน้าซึ่งยืมและเอาต์พุตทั้งสองคือความแตกต่างและยืม

แผนภาพตรรกะตัวลบแบบเต็ม

ตารางความจริงสำหรับ ตัวลบเต็ม คือ

| อินพุต | เอาท์พุต | |||

| X | ย | หยิน | FS_Diff | FS_Borrow |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

ด้วยตารางความจริงข้างต้นแผนภาพวงจรโฆษณาแผนภาพตรรกะสำหรับการใช้งานตัวลบเต็มโดยใช้ตัวลบครึ่งตัวแสดงอยู่ด้านล่าง:

ตัวลบเต็มโดยใช้ HS

ข้อดีและข้อ จำกัด ของตัวลบครึ่งหนึ่ง

ข้อดีของตัวลบครึ่งหนึ่งคือ:

- การใช้งานและการสร้างวงจรนี้ทำได้ง่ายและสะดวก

- วงจรนี้ใช้พลังงานน้อยที่สุดในการประมวลผลสัญญาณดิจิตอล

- ฟังก์ชันการคำนวณสามารถดำเนินการได้ด้วยอัตราความเร็วที่ดีขึ้น

ข้อ จำกัด ของวงจรผสมนี้คือ:

แม้ว่าจะมีการประยุกต์ใช้ตัวลบครึ่งหนึ่งอย่างกว้างขวางในการดำเนินการและฟังก์ชันต่างๆมากมาย แต่ก็มีข้อ จำกัด บางประการ ได้แก่ :

- วงจรลบครึ่งตัวจะไม่ยอมรับ 'ยืมเข้า' จากเอาต์พุตก่อนหน้าซึ่งเป็นข้อเสียเปรียบที่สำคัญของวงจรนี้

- เนื่องจากแอปพลิเคชันแบบเรียลไทม์จำนวนมากทำงานกับการลบจำนวนบิตจำนวนมากอุปกรณ์ตัวลบครึ่งหนึ่งจึงไม่มีความสามารถในการลบบิตจำนวนมาก

แอปพลิเคชันของ Half Subtractor

การประยุกต์ใช้ตัวลบครึ่งหนึ่งมีดังต่อไปนี้

- ตัวลบครึ่งหนึ่งใช้เพื่อลดแรงของสัญญาณเสียงหรือวิทยุ

- มันสามารถ ใช้ในเครื่องขยายเสียง เพื่อลดความผิดเพี้ยนของเสียง

- ตัวลบครึ่งหนึ่งคือ ใช้ใน ALU ของโปรเซสเซอร์

- สามารถใช้เพื่อเพิ่มและลดตัวดำเนินการและคำนวณที่อยู่

- ตัวลบครึ่งหนึ่งใช้เพื่อลบหมายเลขคอลัมน์ที่มีนัยสำคัญน้อยที่สุด สำหรับการลบตัวเลขหลายหลักสามารถใช้สำหรับ LSB

ดังนั้นจากทฤษฎีตัวลบครึ่งหนึ่งข้างต้นในที่สุดเราสามารถปิดมันได้โดยใช้วงจรนี้เราสามารถลบออกจากบิตไบนารีหนึ่งจากอีกบิตหนึ่งเพื่อให้ได้ผลลัพธ์เช่นความแตกต่างและการยืม ในทำนองเดียวกันเราสามารถออกแบบตัวลบครึ่งหนึ่งโดยใช้วงจร NAND gates และ NOR gates แนวคิดอื่น ๆ ที่ควรทราบคืออะไรคือ รหัส verilog ตัวลบครึ่งหนึ่ง และแผนผัง RTL สามารถวาดได้อย่างไร?