ข้อเสียเปรียบหลักของ วงจรผสม คือไม่ใช้หน่วยความจำใด ๆ ในการบันทึกสถานะปัจจุบันและสถานะก่อนหน้า ดังนั้นสถานะก่อนหน้าของอินพุตจึงไม่มีผลใด ๆ ต่อสถานะปัจจุบันของวงจร ในขณะที่วงจรลำดับมีหน่วยความจำดังนั้นเอาต์พุตจึงแตกต่างกันไปตามอินพุต วงจรประเภทนี้ใช้อินพุตเอาต์พุตนาฬิกาและองค์ประกอบหน่วยความจำก่อนหน้า ที่นี่องค์ประกอบหน่วยความจำสามารถสลักหรือรองเท้าแตะ วงจร Sequential ได้รับการออกแบบโดยวิธีการต่างๆเช่นการใช้ ROM และ flips, PLAs, CPLDs (อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซับซ้อน) , FPGAs (อาร์เรย์เกทที่ตั้งโปรแกรมฟิลด์ได้) . ในบทความนี้เราจะพูดถึงวิธีการออกแบบวงจรลำดับโดยใช้ PLA เท่านั้น

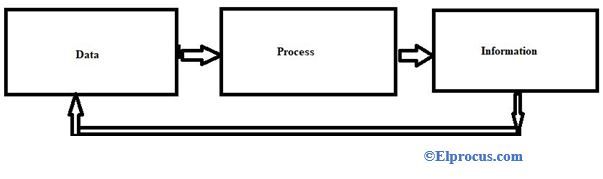

แผนภาพบล็อกของวงจรลำดับดังที่แสดงด้านล่าง:

แผนภาพบล็อกของวงจรลำดับ

การออกแบบวงจรต่อเนื่องโดยใช้ PLA

วงจรลำดับ สามารถรับรู้ได้โดยใช้ PLA (Programmable Logic Arrays) และ flip-flop ในการออกแบบนี้การกำหนดสถานะอาจมีความสำคัญเนื่องจากการใช้การกำหนดสถานะที่ดีสามารถลดจำนวนข้อกำหนดของผลิตภัณฑ์ที่ต้องการได้และด้วยเหตุนี้จึงลดขนาดที่ต้องการของ PLA คำศัพท์ผลิตภัณฑ์ที่กำหนดเป็นการรวมกันของตัวอักษรโดยที่ลิเทอรัลแต่ละตัวเป็นตัวแปรหรือการปฏิเสธ

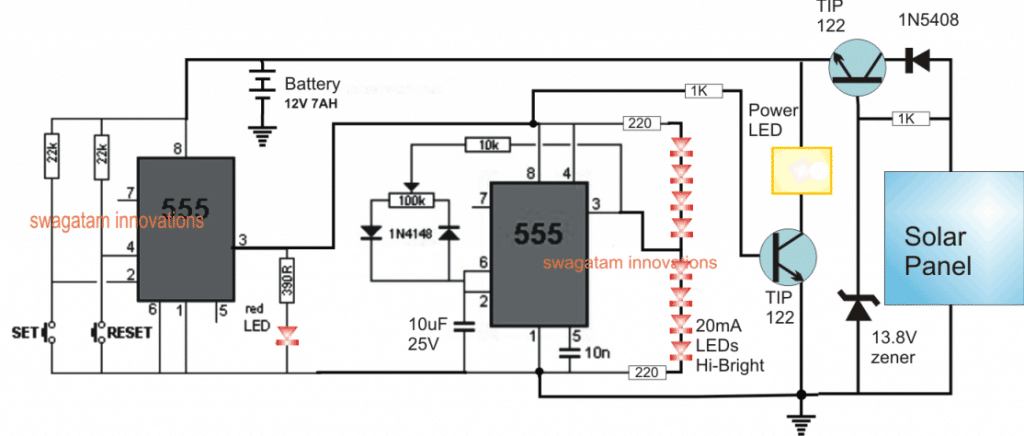

ให้เราพิจารณาการออกแบบตัวแปลงรหัส ตารางสถานะที่แสดงด้านล่างในตารางสามารถรับรู้ได้โดยใช้ PLA หนึ่งตัวและสามตัว รองเท้าแตะ ดังรูปด้านล่าง การกำหนดค่าวงจรนี้คล้ายกับการออกแบบที่ใช้ ROM Flip-Flop มากยกเว้น ROM จะถูกแทนที่ด้วย PLA ที่มีขนาดเหมาะสม การกำหนดสถานะนำไปสู่ตารางความจริงที่ระบุด้านล่าง ตารางนี้สามารถจัดเก็บไว้ใน PLA ที่มีอินพุตสี่ช่องคำศัพท์ผลิตภัณฑ์ 13 รายการและเอาต์พุตสี่ช่อง แต่จะมีขนาดลดลงเล็กน้อยเมื่อเทียบกับ ROM 16 คำ

| X Q1 Q2 Q3 | ด้วย D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

ตาราง: ตารางความจริง

ปัจจุบัน สถานะ

| สถานะถัดไป X = 0 1 | ปัจจุบัน เอาท์พุท (Z) |

| ถึง | ขค | 1 0 |

ข ค | D E. และ E | 1 0 0 1 |

ง คือ | เอช H ม | 0 1 1 0 |

ซ ม | ก ถึง - | 0 1 1 - |

ตาราง: ตารางสถานะ

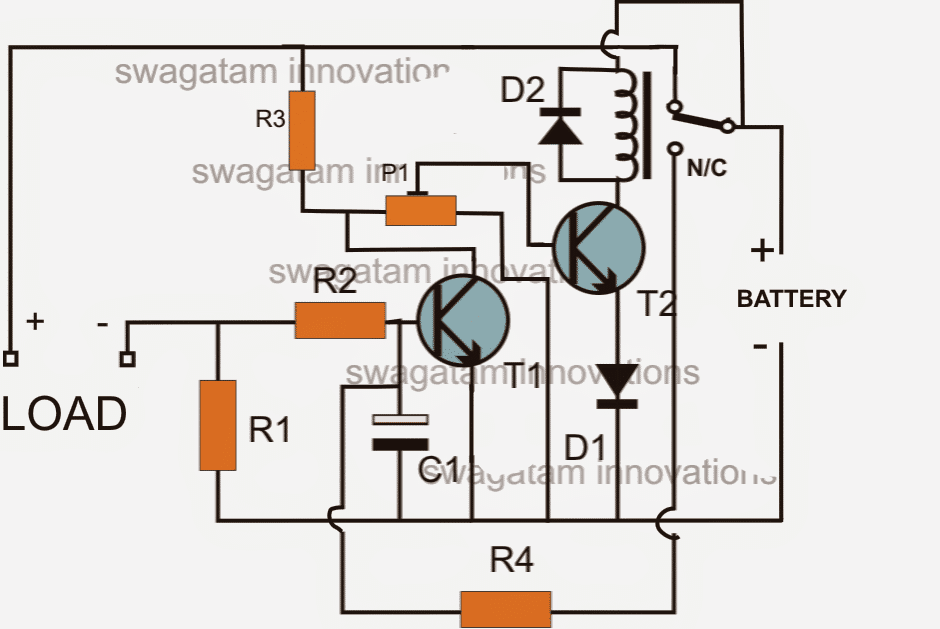

การออกแบบวงจรต่อเนื่องโดยใช้ PLA

สมการอินพุตเอาต์พุตที่ได้รับจาก Karnaugh Map

ที่นี่เนื่องจากมีเจ็ดสถานะจึงจำเป็นต้องมีรองเท้าแตะ D สามตัว ดังนั้นจึงจำเป็นต้องใช้วงจร PLA ที่มี 4 อินพุตและ 4 เอาต์พุต หากมีการพิจารณาการกำหนดสถานะของตัวแปลงรหัสสมการผลลัพธ์ที่ได้และสมการอินพุต D ฟลิปฟล็อปที่ได้มาจาก Karnaugh สามารถเขียนสมการต่อไปนี้

D1 = Q1 + = Q2”

D2 = Q2 + = Q2”

D3 = Q3 + = Q1 Q2 Q3 = X” Q1 Q3” = X Q1” Q2”

Z = X” Q3” + X Q3

| X Q1 Q2 Q3 | ด้วย D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 สิบเอ็ด

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

ตาราง PLA ที่สอดคล้องกับสมการเหล่านี้แสดงไว้ในตารางด้านบน ตารางนี้สามารถรับรู้ได้โดยใช้ PLA ที่มีอินพุตสี่ตัวเงื่อนไขผลิตภัณฑ์เจ็ดคำและเอาต์พุตสี่ตัว ในการตรวจสอบการทำงานของการออกแบบข้างต้นในเบื้องต้นให้สมมติว่า X = 0 และ Q1Q2Q3 = 000 ซึ่งจะเลือกแถว - - 0- และ 0 - - -0 ในตารางดังนั้น Z = 0 และ D1D2D3 = 100 หลังจากขอบนาฬิกาที่ใช้งานอยู่ Q1Q2Q3 = 100 ถ้าอินพุตถัดไปคือ X = 1 แถว - - 0 - และ - 1- - จะถูกเลือกดังนั้น Z = 0 และ D1D2D3 = 110 หลังจากขอบนาฬิกาที่ใช้งานอยู่ Q1Q2Q3 = 110

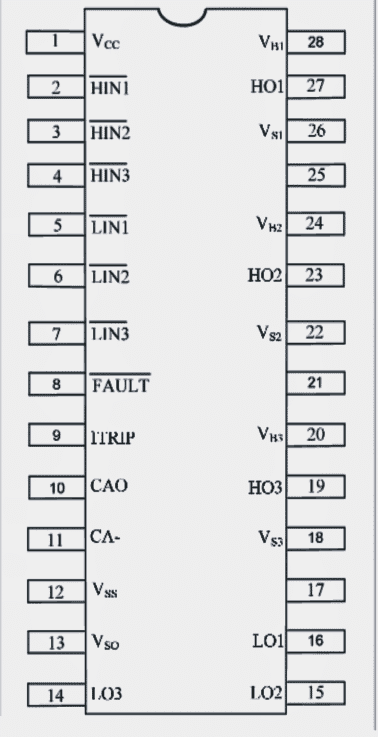

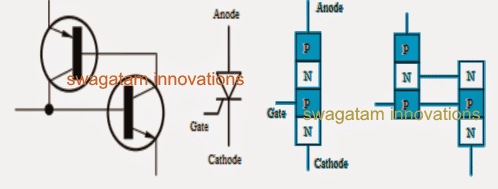

อาร์เรย์ลอจิกที่ตั้งโปรแกรมได้ (PLA)

Programmable Logic Array คืออุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ โดยทั่วไปจะใช้เพื่อใช้วงจรลอจิกเชิงผสม PLA มีชุดของ AND ระนาบที่ตั้งโปรแกรมได้ (AND array) ซึ่งเชื่อมโยงไปยังชุดของเครื่องบินที่ตั้งโปรแกรมได้หรือ (หรืออาร์เรย์) ซึ่งสามารถเสริมได้ชั่วคราวเพื่อสร้างเอาต์พุต เค้าโครงนี้ช่วยให้สามารถสังเคราะห์ฟังก์ชันลอจิกจำนวนมากได้ในไฟล์ ผลรวมของผลิตภัณฑ์ (SOP) รูปแบบบัญญัติ แผนภาพบล็อกอย่างง่ายของ PLA แสดงไว้ด้านล่าง

แผนภาพบล็อกของ PLA

ความแตกต่างหลักระหว่าง PLA และ PAL (ตรรกะอาร์เรย์ที่ตั้งโปรแกรมได้) คือ

ปลา: ทั้งสองอย่าง และเครื่องบินและหรือเครื่องบิน สามารถตั้งโปรแกรมได้

PAL: เฉพาะและเครื่องบินเท่านั้นที่สามารถตั้งโปรแกรมได้ในขณะที่หรือระนาบได้รับการแก้ไข

เพื่อความเข้าใจที่ดีขึ้นเกี่ยวกับ PLA เรากำลังพิจารณาตัวอย่างด้านล่างนี้

ลองนำฟังก์ชันเหล่านี้ไปใช้ f1 และ f2 จะได้รับเป็น

อินพุต x1, x2, x3 และสัญญาณเสริมตามลำดับจะถูกกำหนดให้กับระนาบที่ตั้งโปรแกรมได้และที่นั่นเราจะได้รับเอาต์พุตและระนาบเป็น P1, P2, P3called minterms จากนั้นสัญญาณเหล่านี้จะถูกกำหนดให้กับระนาบที่ตั้งโปรแกรมได้หรือเพื่อสร้างฟังก์ชันเอาต์พุตที่ต้องการ f1 และ f2 (ผลรวมของผลิตภัณฑ์) รูปด้านล่างอธิบายถึงการใช้งานระดับประตูของ PLA สำหรับฟังก์ชันที่กำหนด

การดำเนินการของ PLA

ทั้งหมดนี้เกี่ยวกับการออกแบบวงจรลำดับโดยใช้ PLA เราพิจารณาว่าข้อมูลที่ให้ไว้ในบทความนี้มีประโยชน์สำหรับคุณในการทำความเข้าใจแนวคิดนี้ให้ดีขึ้น นอกจากนี้คำถามใด ๆ เกี่ยวกับบทความนี้หรือความช่วยเหลือใด ๆ การดำเนินโครงการไฟฟ้าและอิเล็กทรอนิกส์ คุณสามารถติดต่อเราได้โดยการแสดงความคิดเห็นในส่วนความคิดเห็นด้านล่าง นี่คือคำถามสำหรับคุณ วงจรซีเควนเชียลหมายถึงอะไร?