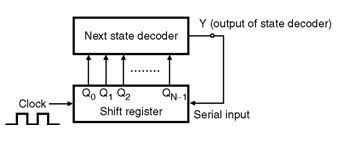

ก่อนหน้านี้การออกแบบของ วงจรลอจิก สามารถทำได้โดยใช้ SSI (บูรณาการขนาดเล็ก) ส่วนประกอบเช่นลอจิกเกต มัลติเพล็กเซอร์ , de-multiplexers, FFs ฯลฯ แต่ตอนนี้ PLD สามารถแทนที่ส่วนประกอบ SSI เหล่านี้ได้ทั้งหมด นี่คือเหตุผลที่ทำให้อุตสาหกรรม SSI ลดลงเมื่อเทียบกับ PLD และสิ่งเหล่านี้ถูกนำไปใช้ในหลายแอปพลิเคชัน อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้หรือ PLD เป็นชิปชนิดหนึ่งที่ใช้ในการสร้างวงจรลอจิก ประกอบด้วยชุดขององค์ประกอบวงจรลอจิกที่สามารถแก้ไขได้หลายวิธี PLD ดูเหมือนกล่องดำที่ประกอบด้วยสวิตช์ที่ตั้งโปรแกรมได้เช่นเดียวกับลอจิกเกต หน้าที่หลักของสวิตช์คือปล่อยให้ลอจิกเกตภายใน PLD เชื่อมโยงกันเพื่อดำเนินการวงจรลอจิก PLD แบ่งออกเป็นประเภทต่างๆเช่น SPLD-simple PLD ( PLA และ PAL ), PLD ซับซ้อน CPLD , FPGA- อาร์เรย์ประตูที่ตั้งโปรแกรมได้ . บทความนี้กล่าวถึงอะไรคือ PAL และ PLA การออกแบบและความแตกต่าง

PAL และ PLA คืออะไร?

ทั้งสอง ลอจิกอาร์เรย์ที่ตั้งโปรแกรมได้ และ อาร์เรย์ลอจิกที่ตั้งโปรแกรมได้ เป็นประเภทของ PLD (อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้) และส่วนใหญ่จะใช้สำหรับการออกแบบตรรกะการรวมกันโดยใช้ลอจิกตามลำดับ ความแตกต่างที่สำคัญระหว่างสองสิ่งนี้คือ PAL สามารถออกแบบโดยใช้คอลเลกชัน AND ประตูและคอลเลกชันที่คงที่ของ OR ประตูในขณะที่ PLA สามารถออกแบบด้วยอาร์เรย์ที่ตั้งโปรแกรมได้ของ AND แม้ว่าจะมีคอลเล็กชัน OR gate แบบคงที่ อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้นำเสนอการออกแบบวงจรลอจิกที่เรียบง่ายและยืดหยุ่น

ลอจิกอาร์เรย์ที่ตั้งโปรแกรมได้

ก่อนหน้านี้เป็นอุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ไฟล์ วงจรลอจิกเชิงผสม สามารถออกแบบด้วยมัลติเพล็กเซอร์และวงจรเหล่านี้มีความแข็งเช่นเดียวกับสารประกอบจากนั้นจึงพัฒนา PLDs อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้เริ่มต้นคือ ROM แต่ไม่ประสบความสำเร็จเนื่องจากปัญหาการสิ้นเปลืองฮาร์ดแวร์รวมถึงการเพิ่มประสิทธิภาพการเติบโตแบบทวีคูณในทุกแอปพลิเคชันฮาร์ดแวร์ เพื่อเอาชนะปัญหานี้จึงใช้ PAL และ PLA ทั้งสองนี้สามารถตั้งโปรแกรมได้และใช้ฮาร์ดแวร์อย่างมีประสิทธิภาพ

อาร์เรย์ลอจิกที่ตั้งโปรแกรมได้

การออกแบบ Array Logic ที่ตั้งโปรแกรมได้ (PAL)

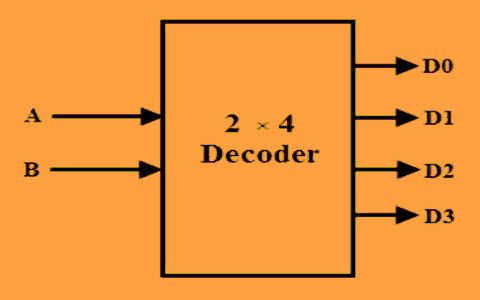

คำจำกัดความของคำว่า PAL หรือ Programmable Array Logic เป็น PLD ประเภทหนึ่งซึ่งเรียกว่าวงจร Programmable Logic Device และการทำงานของ PAL นี้เหมือนกับ PLA การออกแบบลอจิกอาร์เรย์ที่ตั้งโปรแกรมได้สามารถทำได้โดยใช้เกตหรือเกตแบบคงที่และประตู AND ที่ตั้งโปรแกรมได้ ด้วยการใช้สิ่งนี้เราสามารถใช้ฟังก์ชันง่าย ๆ สองฟังก์ชันได้ทุกที่ที่ผู้ร่วมงานและประตูกับประตูหรือแต่ละประตูแสดงถึงจำนวนเงื่อนไขผลิตภัณฑ์สูงสุดที่สามารถผลิตได้ในรูปแบบของ SOP (ผลรวมของผลิตภัณฑ์) ของฟังก์ชันที่แน่นอน

เนื่องจากลอจิกเกตเช่น AND เชื่อมต่ออย่างต่อเนื่องไปยังประตู OR และนั่นบ่งชี้ว่าข้อกำหนดผลิตภัณฑ์ที่ผลิตไม่ได้รับการแจกจ่ายพร้อมกับฟังก์ชันเอาต์พุต แนวคิดหลักที่อยู่เบื้องหลังการพัฒนา PLD คือการสร้างตรรกะบูลีนแบบผสมลงบนชิปตัวเดียวโดยการถอดสายไฟที่มีข้อบกพร่องออกหลีกเลี่ยงการออกแบบลอจิกรวมทั้งลดการใช้พลังงาน

ตัวอย่างของ PAL

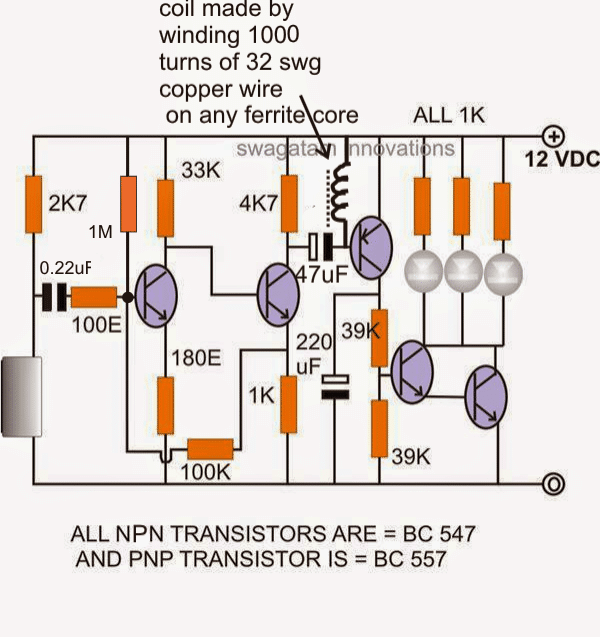

ดำเนินการดังต่อไปนี้ นิพจน์บูลีน ด้วยความช่วยเหลือของ ลอจิกอาร์เรย์ที่ตั้งโปรแกรมได้ (PAL)

X = AB + AC '

Y = AB ’+ BC’

ข้างต้นให้สอง ฟังก์ชันบูลีน อยู่ในรูปแบบของ SOP (ผลรวมของผลิตภัณฑ์) . คำศัพท์ผลิตภัณฑ์ที่มีอยู่ในนิพจน์บูลีนคือ X & Y และคำศัพท์ผลิตภัณฑ์หนึ่งคำที่เป็น AC 'จะพบได้บ่อยในทุกสมการ ดังนั้นลอจิกเกตที่จำเป็นทั้งหมดสำหรับการสร้างสองสมการข้างต้นคือและประตู -4 หรือประตูที่ตั้งโปรแกรมได้ -2 แผนภาพตรรกะ PAL ที่เทียบเท่าจะแสดงไว้ด้านล่าง

วงจรลอจิก PAL

ประตู AND ที่ตั้งโปรแกรมได้มีสิทธิ์ในการป้อนข้อมูลสำหรับอินพุตตัวแปรปกติและแบบเสริม ในแผนภาพลอจิกด้านบนอินพุตที่ใช้ได้สำหรับแต่ละเกตคือ A, A ’, B, B’, C, C ’ ดังนั้นในการสร้างคำศัพท์ผลิตภัณฑ์เดียวกับทุกประตู AND จึงจำเป็นต้องมีโปรแกรม

ข้อกำหนดผลิตภัณฑ์ทั้งหมดสามารถหาได้จากอินพุตของแต่ละประตูหรือ ที่นี่การเชื่อมต่อที่ตั้งโปรแกรมได้บนลอจิกเกตสามารถแสดงด้วยสัญลักษณ์ ‘X’

ที่นี่อินพุตหรือประตูได้รับการแก้ไข ดังนั้นข้อกำหนดผลิตภัณฑ์ที่ต้องการจึงเชื่อมโยงกับอินพุตหรือเกตแต่ละรายการ ด้วยเหตุนี้ประตูเหล่านี้จะสร้างสมการบูลีนโดยเฉพาะ '.' สัญลักษณ์แสดงถึงการเชื่อมต่อแบบถาวร

การออกแบบอาร์เรย์ลอจิกที่ตั้งโปรแกรมได้ (PLA)

คำจำกัดความของคำว่า PLA นำเสนอฟังก์ชันบูลีนในรูปของผลรวมของผลิตภัณฑ์ (SOP) การออกแบบอาร์เรย์ลอจิกที่ตั้งโปรแกรมได้นี้สามารถทำได้โดยใช้ลอจิกเกตเช่น AND, OR และไม่ใช่โดยการประดิษฐ์บนชิปซึ่งจะทำให้ทุกอินพุตและคำชมเชยสามารถหาได้จากทุกประตู AND

เอาต์พุตของ AND ทุกประตูเชื่อมต่อกับทุกประตู OR ในที่สุดเอาต์พุตของ OR gate จะสร้างเอาต์พุตของชิป ดังนั้นนี่คือวิธีที่การเชื่อมโยงที่เหมาะสมเสร็จสิ้นเพื่อใช้นิพจน์ของผลรวมของผลิตภัณฑ์ ในอาร์เรย์ลอจิกที่ตั้งโปรแกรมได้การเชื่อมต่อของลอจิกเกตเช่น AND & OR สามารถตั้งโปรแกรมได้ PLA มีราคาแพงและยากที่จะเปรียบเทียบกับ PAL PAL ใช้วิธีการพัฒนาที่แตกต่างกันสองวิธีที่สามารถใช้สำหรับอาร์เรย์ลอจิกที่ตั้งโปรแกรมได้เพื่อเพิ่มความสะดวกในการเขียนโปรแกรม ในวิธีการนี้การเชื่อมต่อทุกครั้งสามารถทำได้โดยใช้ฟิวส์ที่จุดตัดแต่ละจุดที่จุดเชื่อมต่อที่ไม่จำเป็นออกโดยการเป่าฟิวส์ เทคนิคสุดท้ายเกี่ยวข้องกับการสร้างการเชื่อมต่อในขณะที่ขั้นตอนการประดิษฐ์โดยใช้ฝาครอบที่เหมาะสมสำหรับรูปแบบการเชื่อมต่อที่แม่นยำ

ตัวอย่าง PLA

ใช้นิพจน์บูลีนต่อไปนี้ด้วยความช่วยเหลือของอาร์เรย์ลอจิกที่ตั้งโปรแกรมได้ (PLA)

X = AB + AC '

Y = AB '+ BC + AC'

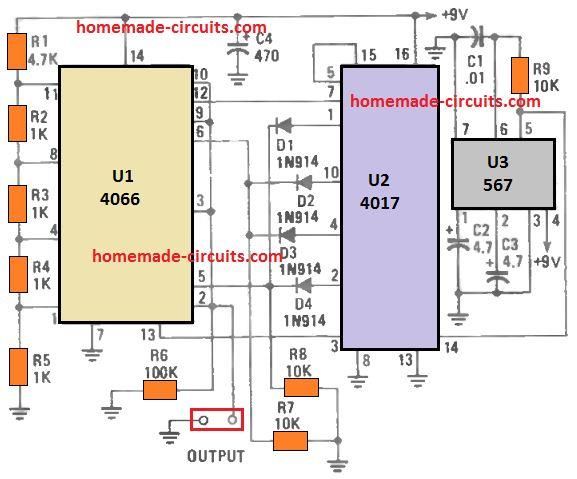

ฟังก์ชันบูลีนสองฟังก์ชันที่กำหนดข้างต้นอยู่ในรูปแบบของ SOP (ผลรวมของผลิตภัณฑ์) คำศัพท์ผลิตภัณฑ์ที่มีอยู่ในนิพจน์บูลีนคือ X & Y และคำศัพท์ผลิตภัณฑ์หนึ่งคำที่เป็น AC 'จะพบได้บ่อยในทุกสมการ ดังนั้นลอจิกเกตที่จำเป็นทั้งหมดสำหรับการสร้างสองสมการข้างต้นคือและประตู -4 หรือที่ตั้งโปรแกรมได้หรือประตู -2 แผนภาพตรรกะ PLA ที่เทียบเท่าแสดงอยู่ด้านล่าง

วงจรลอจิกของปลา

ประตู AND ที่ตั้งโปรแกรมได้มีสิทธิ์ในการป้อนข้อมูลสำหรับอินพุตตัวแปรปกติและแบบเสริม ในแผนภาพลอจิกด้านบนอินพุตที่ใช้ได้สำหรับแต่ละเกตคือ A, A ’, B, B’, C, C ’ ดังนั้นในการสร้างคำศัพท์ผลิตภัณฑ์เดียวกับทุกประตู AND จึงจำเป็นต้องมีโปรแกรม

เงื่อนไขผลิตภัณฑ์ทั้งหมดสามารถหาได้จากอินพุตของแต่ละประตูหรือ ที่นี่การเชื่อมต่อที่ตั้งโปรแกรมได้บนลอจิกเกตสามารถแสดงด้วยสัญลักษณ์ ‘X’

ความแตกต่างระหว่าง PAL และ PLA

ความแตกต่างระหว่าง PAL และ PLA ในรูปแบบตาราง ส่วนใหญ่รวมถึง PAL และ PLA แบบเต็ม , การก่อสร้าง, ความพร้อมใช้งาน, ความยืดหยุ่น, ต้นทุน, จำนวนฟังก์ชันและความเร็วซึ่งจะกล่าวถึงด้านล่าง

| ลอจิกอาร์เรย์ที่ตั้งโปรแกรมได้ (PAL) | อาร์เรย์ลอจิกที่ตั้งโปรแกรมได้ (PLA) |

| PAL แบบเต็มคือลอจิกอาร์เรย์ที่ตั้งโปรแกรมได้ | PLA เต็มรูปแบบคืออาร์เรย์ลอจิกที่ตั้งโปรแกรมได้ |

| การสร้าง PAL สามารถทำได้โดยใช้คอลเลคชัน AND & OR ที่ตั้งโปรแกรมได้ | การสร้าง PLA สามารถทำได้โดยใช้คอลเลกชัน AND และคอลเลกชันคงที่ของ OR ประตู |

| ความพร้อมใช้งานของ PAL นั้นอุดมสมบูรณ์น้อยกว่า | ความพร้อมของ PLA มีมากขึ้น |

| ความยืดหยุ่นของการเขียนโปรแกรม PAL มีมากขึ้น | ความยืดหยุ่นของ PLA น้อยลง |

| ค่า PAL แพง | ค่าใช้จ่ายของ PLA อยู่ในช่วงกลาง |

| จำนวนฟังก์ชันที่ใช้ใน PAL มีมาก | จำนวนฟังก์ชันที่ใช้ใน PLA มี จำกัด |

| ความเร็วของ PAL ช้า | ความเร็วของ PLA สูง |

ดังนั้นทั้งหมดนี้จึงเกี่ยวกับ PAL และ PLA จากข้อมูลข้างต้นในที่สุดเราสามารถสรุปได้ว่าสิ่งเหล่านี้คืออุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ (PLDs) โดยที่ อาร์เรย์ลอจิกที่ตั้งโปรแกรมได้ มีความยืดหยุ่นมากกว่าตรรกะของอาร์เรย์ที่ตั้งโปรแกรมได้ แต่ลอจิกอาร์เรย์ที่ตั้งโปรแกรมได้สามารถสร้างวงจรลอจิกเชิงผสมได้อย่างง่ายดาย นี่คือคำถามสำหรับคุณบทบาทของคืออะไร PAL และ PLA ใน Digital Electronics เหรอ?