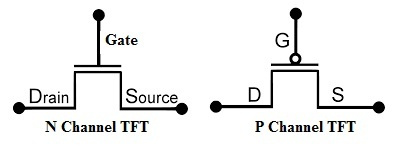

คำว่า CMOS ย่อมาจาก“ Complementary Metal Oxide Semiconductor” นี่เป็นหนึ่งในเทคโนโลยีที่ได้รับความนิยมมากที่สุดในอุตสาหกรรมการออกแบบชิปคอมพิวเตอร์และมีการใช้กันอย่างแพร่หลายในปัจจุบัน วงจรรวม ในการใช้งานมากมายและหลากหลาย ความทรงจำของคอมพิวเตอร์ซีพียูและโทรศัพท์มือถือในปัจจุบันใช้ประโยชน์จากเทคโนโลยีนี้เนื่องจากข้อดีที่สำคัญหลายประการ เทคโนโลยีนี้ใช้อุปกรณ์เซมิคอนดักเตอร์ทั้ง P channel และ N channel หนึ่งในเทคโนโลยี MOSFET ที่ได้รับความนิยมมากที่สุดในปัจจุบันคือเทคโนโลยี Complementary MOS หรือ CMOS นี่คือเทคโนโลยีเซมิคอนดักเตอร์ที่โดดเด่นสำหรับไมโครโปรเซสเซอร์ชิปไมโครคอนโทรลเลอร์หน่วยความจำเช่น RAM, ROM, EEPROM และ วงจรรวมเฉพาะแอปพลิเคชัน (ASIC)

รู้เบื้องต้นเกี่ยวกับเทคโนโลยี MOS

ในการออกแบบ IC ส่วนประกอบพื้นฐานและจำเป็นที่สุดคือทรานซิสเตอร์ มอสเฟตจึงเป็นทรานซิสเตอร์ชนิดหนึ่งที่ใช้ในหลาย ๆ แอพพลิเคชั่น การก่อตัวของทรานซิสเตอร์นี้สามารถทำได้เหมือนแซนวิชโดยรวมชั้นเซมิคอนดักเตอร์โดยทั่วไปคือเวเฟอร์ชิ้นจากซิลิกอนผลึกเดียวชั้นซิลิกอนไดออกไซด์และชั้นโลหะ ชั้นเหล่านี้อนุญาตให้เกิดทรานซิสเตอร์ขึ้นภายในวัสดุเซมิคอนดักเตอร์ ฉนวนที่ดีเช่น Sio2 มีชั้นบาง ๆ ที่มีความหนาเป็นร้อยโมเลกุล

ทรานซิสเตอร์ที่เราใช้ polycrystalline silicon (poly) แทนโลหะสำหรับส่วนประตู ประตูโพลีซิลิคอนของ FET สามารถเปลี่ยนได้เกือบโดยใช้ประตูโลหะใน IC ขนาดใหญ่ บางครั้งทั้งโพลีซิลิคอนและโลหะ FET เรียกว่า IGFET ซึ่งหมายถึงฉนวนประตู FET เนื่องจาก Sio2 ด้านล่างประตูเป็นฉนวน

CMOS (เซมิคอนดักเตอร์โลหะออกไซด์เสริม)

หลัก ข้อได้เปรียบของ CMOS มากกว่า NMOS และเทคโนโลยี BIPOLAR เป็นการกระจายพลังงานที่น้อยกว่ามาก ไม่เหมือนกับวงจร NMOS หรือ BIPOLAR วงจร Complementary MOS แทบจะไม่มีการกระจายกำลังไฟฟ้าสถิตย์ กำลังจะกระจายไปในกรณีที่วงจรสวิทช์จริงเท่านั้น สิ่งนี้ช่วยให้สามารถรวมประตู CMOS บน IC ได้มากกว่าใน NMOS หรือ เทคโนโลยีสองขั้ว ส่งผลให้ประสิทธิภาพดีขึ้นมาก ทรานซิสเตอร์เซมิคอนดักเตอร์ของ Metal Oxide ประกอบด้วย P-channel MOS (PMOS) และ N-channel MOS (NMOS) โปรดดูลิงก์เพื่อทราบข้อมูลเพิ่มเติม กระบวนการผลิตทรานซิสเตอร์ CMOS .

CMOS (เซมิคอนดักเตอร์โลหะออกไซด์เสริม)

NMOS

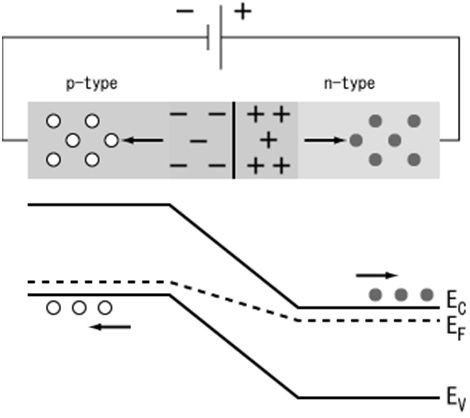

NMOS สร้างขึ้นบนวัสดุพิมพ์ชนิด p ที่มีแหล่งกำเนิดชนิด n และท่อระบายน้ำกระจายอยู่ ใน NMOS ผู้ให้บริการส่วนใหญ่เป็นอิเล็กตรอน เมื่อไฟฟ้าแรงสูงถูกนำไปใช้กับประตู NMOS จะดำเนินการ ในทำนองเดียวกันเมื่อใช้แรงดันไฟฟ้าต่ำกับประตู NMOS จะไม่ทำงาน NMOS ถือว่าเร็วกว่า PMOS เนื่องจากพาหะใน NMOS ซึ่งเป็นอิเล็กตรอนเดินทางเร็วกว่ารูสองเท่า

ทรานซิสเตอร์ NMOS

PMOS

P-channel MOSFET ประกอบด้วย P-type Source และ Drain ที่กระจายอยู่บนวัสดุพิมพ์ชนิด N พาหะส่วนใหญ่เป็นหลุม เมื่อใช้ไฟฟ้าแรงสูงกับประตู PMOS จะไม่ทำงาน เมื่อใช้แรงดันไฟฟ้าต่ำกับประตู PMOS จะดำเนินการ อุปกรณ์ PMOS มีภูมิคุ้มกันต่อเสียงรบกวนมากกว่าอุปกรณ์ NMOS

PMOS ทรานซิสเตอร์

หลักการทำงานของ CMOS

ในเทคโนโลยี CMOS จะใช้ทรานซิสเตอร์ทั้งชนิด N และชนิด P ในการออกแบบฟังก์ชันลอจิก สัญญาณเดียวกับที่เปิดทรานซิสเตอร์ประเภทหนึ่งใช้เพื่อปิดทรานซิสเตอร์อีกประเภทหนึ่ง คุณลักษณะนี้ช่วยให้สามารถออกแบบอุปกรณ์ลอจิกโดยใช้สวิตช์ธรรมดาเท่านั้นโดยไม่ต้องใช้ตัวต้านทานแบบดึงขึ้น

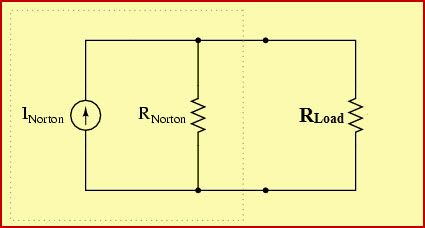

ใน CMOS ประตูตรรกะ คอลเลกชันของ MOSFET ชนิด n ถูกจัดเรียงไว้ในเครือข่ายแบบดึงลงระหว่างเอาต์พุตและรางจ่ายไฟแรงดันต่ำ (Vss หรือสายดินค่อนข้างบ่อย) แทนที่จะเป็นตัวต้านทานโหลดของลอจิกเกต NMOS ลอจิกเกต CMOS จะมีคอลเลกชันของ MOSFET ชนิด p ในเครือข่ายแบบดึงขึ้นระหว่างเอาต์พุตและรางแรงดันไฟฟ้าที่สูงขึ้น (มักเรียกว่า Vdd)

CMOS โดยใช้ Pull Up & Pull Down

ดังนั้นหากทรานซิสเตอร์ทั้งชนิด p และชนิด n มีประตูเชื่อมต่อกับอินพุตเดียวกัน MOSFET ชนิด p จะเปิดเมื่อ MOSFET ชนิด n ปิดอยู่และในทางกลับกัน เครือข่ายจะถูกจัดเรียงให้เครือข่ายเปิดอยู่และอีกเครือข่ายหนึ่งปิดสำหรับรูปแบบการป้อนข้อมูลใด ๆ ดังแสดงในรูปด้านล่าง

CMOS มีความเร็วค่อนข้างสูงการกระจายพลังงานต่ำขอบสัญญาณรบกวนสูงในทั้งสองสถานะและจะทำงานในช่วงแรงดันไฟฟ้าต้นทางและอินพุตที่หลากหลาย (หากแรงดันไฟฟ้าของแหล่งจ่ายคงที่) นอกจากนี้เพื่อความเข้าใจที่ดีขึ้นเกี่ยวกับหลักการทำงานของ Complementary Metal Oxide Semiconductor เราจำเป็นต้องพูดคุยสั้น ๆ เกี่ยวกับลอจิกเกต CMOS ดังที่อธิบายไว้ด้านล่าง

อุปกรณ์ใดใช้ CMOS

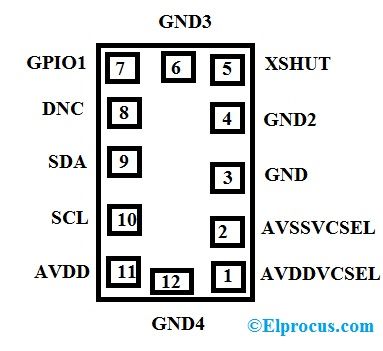

เทคโนโลยีเช่น CMOS ใช้ในชิปต่างๆเช่นไมโครคอนโทรลเลอร์ไมโครโปรเซสเซอร์ SRAM (แรมแบบคงที่) และวงจรลอจิกดิจิทัลอื่น ๆ เทคโนโลยีนี้ใช้ในวงจรอะนาล็อกที่หลากหลายซึ่งรวมถึงตัวแปลงข้อมูลเซ็นเซอร์ภาพและตัวรับส่งสัญญาณที่รวมเข้าด้วยกันสำหรับการสื่อสารหลายประเภท

อินเวอร์เตอร์ CMOS

วงจรอินเวอร์เตอร์ดังแสดงในรูปด้านล่าง มันประกอบด้วย PMOS และ NMOS FET . อินพุต A ทำหน้าที่เป็นแรงดันเกตสำหรับทรานซิสเตอร์ทั้งสอง

ทรานซิสเตอร์ NMOS มีอินพุตจาก Vss (กราวด์) และทรานซิสเตอร์ PMOS มีอินพุตจาก Vdd เอาต์พุตขั้ว Y เมื่อให้แรงดันไฟฟ้าสูง (~ Vdd) ที่ขั้วอินพุต (A) ของอินเวอร์เตอร์ PMOS จะกลายเป็นวงจรเปิดและ NMOS จะปิดดังนั้นเอาต์พุตจะถูกดึงลงไปที่ Vss

อินเวอร์เตอร์ CMOS

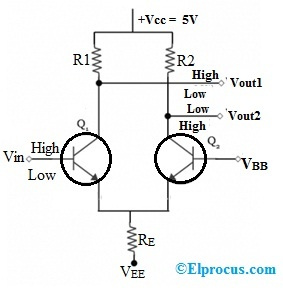

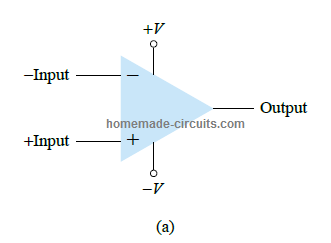

เมื่อแรงดันไฟฟ้าระดับต่ำ ( รูปด้านล่างแสดงเกต MOS NAND เสริมแบบ 2 อินพุต ประกอบด้วยทรานซิสเตอร์ NMOS สองชุดระหว่าง Y และกราวด์และทรานซิสเตอร์ PMOS แบบขนานสองตัวระหว่าง Y และ VDD หากอินพุต A หรือ B เป็นลอจิก 0 ทรานซิสเตอร์ NMOS อย่างน้อยหนึ่งตัวจะถูกปิดซึ่งจะทำลายเส้นทางจาก Y ไปยังกราวด์ แต่อย่างน้อยหนึ่งในทรานซิสเตอร์ pMOS จะเปิดอยู่โดยสร้างเส้นทางจาก Y ไปยัง VDD ประตู NAND สองอินพุต ดังนั้นเอาต์พุต Y จะสูง หากอินพุตทั้งสองมีค่าสูงทรานซิสเตอร์ nMOS ทั้งสองจะเปิดอยู่และทรานซิสเตอร์ pMOS ทั้งสองจะปิด ดังนั้นผลลัพธ์จะอยู่ในระดับต่ำ ตารางความจริงของลอจิกเกต NAND ที่ระบุในตารางด้านล่าง ประตู NOR 2 อินพุตแสดงในรูปด้านล่าง ทรานซิสเตอร์ NMOS จะขนานกันเพื่อดึงเอาท์พุทให้ต่ำเมื่ออินพุตสูง ทรานซิสเตอร์ PMOS อยู่ในอนุกรมเพื่อดึงเอาท์พุทให้สูงเมื่ออินพุตทั้งสองอยู่ต่ำดังที่ระบุในตารางด้านล่าง ผลผลิตจะไม่ถูกปล่อยให้ลอยอยู่ สองประตูอินพุต NOR ตารางความจริงของประตูลอจิก NOR ที่ระบุไว้ในตารางด้านล่าง การประดิษฐ์ทรานซิสเตอร์ CMOS สามารถทำได้บนเวเฟอร์ซิลิกอน เส้นผ่านศูนย์กลางของเวเฟอร์มีตั้งแต่ 20 มม. ถึง 300 มม. ในการนี้กระบวนการพิมพ์หินจะเหมือนกับแท่นพิมพ์ ในทุกขั้นตอนสามารถฝากวัสดุที่แตกต่างกันแกะสลักลวดลายเป็นอย่างอื่นได้ กระบวนการนี้เข้าใจง่ายมากโดยการดูด้านบนของเวเฟอร์และส่วนตัดขวางภายในวิธีการประกอบที่เรียบง่าย การประดิษฐ์ CMOS สามารถทำได้โดยใช้เทคโนโลยีสามอย่าง ได้แก่ N-well pt P-well, Twin well, SOI (Silicon on Insulator) โปรดดูลิงก์นี้เพื่อทราบข้อมูลเพิ่มเติม การผลิต CMOS . อายุการใช้งานโดยทั่วไปของแบตเตอรี่ CMOS คือประมาณ 10 ปี แต่สิ่งนี้สามารถเปลี่ยนแปลงได้ขึ้นอยู่กับการใช้ประโยชน์และสภาพแวดล้อมทุกที่ที่พีซีอยู่ เมื่อแบตเตอรี่ CMOS ล้มเหลวแสดงว่าคอมพิวเตอร์ไม่สามารถรักษาเวลาและวันที่ที่แน่นอนบนคอมพิวเตอร์ได้เมื่อปิดเครื่อง ตัวอย่างเช่นเมื่อคอมพิวเตอร์เปิดอยู่คุณอาจเห็นเวลาและวันที่เช่น 12:00 PM และ 1 มกราคม 1990 ข้อผิดพลาดนี้ระบุว่าแบตเตอรี่ของ CMOS ล้มเหลว ลักษณะที่สำคัญที่สุดของ CMOS คือการใช้พลังงานไฟฟ้าสถิตย์ต่ำมีภูมิคุ้มกันเสียงรบกวนมาก เมื่อทรานซิสเตอร์ตัวเดียวจากคู่ของทรานซิสเตอร์ MOSFET ถูกปิดการรวมกันของชุดจะใช้พลังงานที่สำคัญตลอดการสลับระหว่างทั้งสองที่ระบุไว้เช่นเปิดและปิด ด้วยเหตุนี้อุปกรณ์เหล่านี้จึงไม่สร้างความร้อนทิ้งเมื่อเทียบกับวงจรลอจิกประเภทอื่น ๆ เช่นลอจิก TTL หรือ NMOS ซึ่งโดยปกติจะใช้กระแสไฟฟ้านิ่งแม้ว่าจะไม่เปลี่ยนสถานะก็ตาม คุณลักษณะ CMOS เหล่านี้จะช่วยให้สามารถรวมฟังก์ชันลอจิกที่มีความหนาแน่นสูงบนวงจรรวมได้ ด้วยเหตุนี้ CMOS จึงกลายเป็นเทคโนโลยีที่ใช้บ่อยที่สุดในการดำเนินการภายในชิป VLSI วลี MOS เป็นการอ้างอิงถึงโครงสร้างทางกายภาพของ MOSFET ซึ่งรวมถึงอิเล็กโทรดที่มีประตูโลหะซึ่งอยู่ด้านบนของฉนวนออกไซด์ของวัสดุเซมิคอนดักเตอร์ วัสดุอย่างอลูมิเนียมถูกใช้เพียงครั้งเดียว แต่ตอนนี้วัสดุเป็นโพลีซิลิคอน การออกแบบประตูโลหะอื่น ๆ สามารถทำได้โดยใช้การกลับมาของวัสดุอิเล็กทริกสูงภายในกระบวนการของกระบวนการ CMOS เซ็นเซอร์ภาพเช่นอุปกรณ์คู่ประจุไฟฟ้า (CCD) และโลหะ - ออกไซด์ - เซมิคอนดักเตอร์เสริม (CMOS) เป็นเทคโนโลยีสองประเภทที่แตกต่างกัน สิ่งเหล่านี้ใช้เพื่อจับภาพแบบดิจิทัล เซนเซอร์ภาพทุกตัวมีข้อดีข้อเสียและการใช้งาน ความแตกต่างหลักระหว่าง CCD และ CMOS คือวิธีการจับภาพเฟรม อุปกรณ์ชาร์จไฟอย่าง CCD ใช้ชัตเตอร์ทั่วโลกในขณะที่ CMOS ใช้ชัตเตอร์กลิ้ง เซ็นเซอร์ภาพทั้งสองนี้เปลี่ยนประจุจากแสงเป็นไฟฟ้าและประมวลผลเป็นสัญญาณอิเล็กทรอนิกส์ กระบวนการผลิตที่ใช้ใน CCD มีความพิเศษในการสร้างความสามารถในการเคลื่อนย้ายประจุไฟฟ้าไปทั่ว IC โดยไม่มีการเปลี่ยนแปลง ดังนั้นกระบวนการผลิตนี้สามารถนำไปสู่เซ็นเซอร์ที่มีคุณภาพสูงมากเกี่ยวกับความไวแสงและความเที่ยงตรง ในทางตรงกันข้ามชิป CMOS ใช้ขั้นตอนการผลิตแบบคงที่ในการออกแบบชิปและสามารถใช้กระบวนการที่คล้ายกันในการสร้างไมโครโปรเซสเซอร์ได้ เนื่องจากความแตกต่างในการผลิตจึงมีความแตกต่างที่ชัดเจนระหว่างเซ็นเซอร์เช่น CCD 7 CMOS เซ็นเซอร์ CCD จะจับภาพที่มีสัญญาณรบกวนน้อยและมีคุณภาพมากในขณะที่เซ็นเซอร์ CMOS มักจะมีสัญญาณรบกวนมากกว่า โดยปกติ CMOS จะใช้พลังงานน้อยกว่าในขณะที่ CCD ใช้พลังงานมากมายเช่นเซ็นเซอร์ CMOS มากกว่า 100 เท่า การผลิตชิป CMOS สามารถทำได้ในสายการผลิต Si ทั่วไปเนื่องจากมีราคาถูกมากเมื่อเทียบกับ CCD เซ็นเซอร์ CCD มีความเป็นผู้ใหญ่มากขึ้นเนื่องจากมีการผลิตจำนวนมากเป็นระยะเวลานาน ทั้งตัวสร้างภาพ CMOS และ CCD ขึ้นอยู่กับเอฟเฟกต์ของโฟโตอิเล็กทริคในการสร้างสัญญาณไฟฟ้าจากแสง จากความแตกต่างข้างต้น CCD ถูกใช้ในกล้องเพื่อกำหนดเป้าหมายภาพคุณภาพสูงผ่านพิกเซลจำนวนมากและความไวแสงที่โดดเด่น โดยปกติเซ็นเซอร์ CMOS จะมีความละเอียดคุณภาพและความไวน้อยกว่า สลักขึ้นสามารถกำหนดได้ว่าเมื่อไฟฟ้าลัดวงจรเกิดขึ้นระหว่างขั้วทั้งสองเช่นกำลังและกราวด์เพื่อให้สามารถสร้างกระแสไฟฟ้าสูงและ IC อาจเสียหายได้ ใน CMOS การสลักขึ้นคือการเกิดเส้นทางอิมพีแดนซ์ต่ำระหว่างรางไฟฟ้าและรางพื้นเนื่องจากการสื่อสารระหว่างทรานซิสเตอร์สองตัวเช่น PNP & NPN แบบกาฝาก ทรานซิสเตอร์ . ในวงจร CMOS ทรานซิสเตอร์สองตัวเช่น PNP & NPN เชื่อมต่อกับรางจ่ายสองตัวเช่น VDD & GND การป้องกันทรานซิสเตอร์เหล่านี้ทำได้ผ่านตัวต้านทาน ในการส่งแบบสลักกระแสไฟฟ้าจะไหลจาก VDD ไปยัง GND ตรงผ่านทรานซิสเตอร์สองตัวเพื่อให้เกิดไฟฟ้าลัดวงจรได้ดังนั้นกระแสไฟฟ้าที่รุนแรงจะไหลจาก VDD ไปยังขั้วกราวด์ มีวิธีการต่างๆในการป้องกันการล็อค ในการป้องกันการสลักสามารถวางความต้านทานสูงในเส้นทางเพื่อหยุดการไหลของกระแสไฟฟ้าตลอดทั้งอุปทาน & เพื่อให้β1 * β2ต่ำกว่า 1 โดยใช้วิธีการต่อไปนี้ โครงสร้างของ SCR ปรสิตจะถูกทำลายโดยรอบของทรานซิสเตอร์เช่น PMOS และ NMOS ผ่านชั้นออกไซด์ที่เป็นฉนวน เทคโนโลยีสำหรับการป้องกันการล็อกจะปิดอุปกรณ์เมื่อสังเกตเห็นการล็อก บริการทดสอบการสลักสามารถทำได้โดยผู้ขายจำนวนมากในตลาด การทดสอบนี้สามารถทำได้โดยลำดับความพยายามในการเปิดใช้งานโครงสร้างของ SCR ใน CMOS IC ในขณะที่พินที่เกี่ยวข้องจะถูกตรวจสอบเมื่อกระแสเกินไหลผ่าน ขอแนะนำให้รับตัวอย่างแรกจากล็อตทดลองและส่งไปยังห้องปฏิบัติการทดสอบของ Latch-up ห้องปฏิบัติการนี้จะใช้แหล่งจ่ายไฟที่สามารถทำได้สูงสุดจากนั้นจัดหาแหล่งจ่ายกระแสไฟฟ้าให้กับอินพุตและเอาต์พุตของชิปเมื่อใดก็ตามที่เกิด Latch-up ขึ้นผ่านการตรวจสอบแหล่งจ่ายกระแส ข้อดีของ CMOS มีดังต่อไปนี้ ประโยชน์หลักของ CMOS ผ่าน TTL คืออัตราสัญญาณรบกวนที่ดีและใช้พลังงานน้อยลง เนื่องจากไม่มีช่องทางเดินตรงจาก VDD ถึง GND เวลาตกขึ้นอยู่กับเงื่อนไขของอินพุตดังนั้นการส่งสัญญาณดิจิทัลจะกลายเป็นเรื่องง่ายและต้นทุนต่ำผ่านชิป CMOS CMOS ใช้เพื่ออธิบายจำนวนหน่วยความจำบนเมนบอร์ดของคอมพิวเตอร์ที่จะจัดเก็บในการตั้งค่าของ BIOS การตั้งค่าเหล่านี้ส่วนใหญ่รวมถึงวันที่เวลาและการตั้งค่าฮาร์ดแวร์ ผลลัพธ์จะออกมาหากไดรฟ์ CMOS ทำงานได้ทั้งสองวิธี ข้อเสียของ CMOS มีดังต่อไปนี้ กระบวนการ MOS เสริมถูกนำไปใช้อย่างกว้างขวางและได้ถูกแทนที่โดยพื้นฐานแล้ว NMOS และกระบวนการสองขั้วสำหรับแอปพลิเคชันลอจิกดิจิทัลเกือบทั้งหมด เทคโนโลยี CMOS ถูกนำมาใช้สำหรับการออกแบบ IC ดิจิทัลต่อไปนี้ ดังนั้นไฟล์ ทรานซิสเตอร์ CMOS มีชื่อเสียงมาก เนื่องจากใช้พลังงานไฟฟ้าอย่างมีประสิทธิภาพ พวกเขาไม่ใช้แหล่งจ่ายไฟเมื่อใดก็ตามที่มีการเปลี่ยนแปลงจากเงื่อนไขหนึ่งไปเป็นอีกเงื่อนไขหนึ่ง นอกจากนี้เซมิคอนดักเตอร์ฟรียังทำงานร่วมกันเพื่อหยุดแรงดันไฟฟ้า o / p ผลลัพธ์คือการออกแบบที่ใช้พลังงานต่ำซึ่งให้ความร้อนน้อยลงด้วยเหตุนี้ทรานซิสเตอร์เหล่านี้จึงเปลี่ยนการออกแบบอื่น ๆ ก่อนหน้านี้เช่น CCD ภายในเซ็นเซอร์กล้องและใช้ในโปรเซสเซอร์ปัจจุบันส่วนใหญ่ หน่วยความจำของ CMOS ภายในคอมพิวเตอร์เป็นแรมชนิดไม่ลบเลือนซึ่งเก็บการตั้งค่า BIOS และข้อมูลของเวลาและวันที่ ฉันเชื่อว่าคุณมีความเข้าใจในแนวคิดนี้ดีขึ้น นอกจากนี้ข้อสงสัยใด ๆ เกี่ยวกับแนวคิดนี้หรือ โครงการอิเล็กทรอนิกส์ โปรดให้ข้อเสนอแนะที่มีค่าของคุณโดยการแสดงความคิดเห็นในส่วนความคิดเห็นด้านล่าง นี่คือคำถามสำหรับคุณทำไม CMOS จึงดีกว่า NMOS? อินพุต อินพุตลอจิก เอาท์พุท เอาท์พุทตรรกะ 0 โวลต์ 0 Vdd 1 Vdd 1 0 โวลต์ 0 ประตู CMOS NAND

ถึง ข เครือข่ายแบบดึงลง Pull-up Network เอาท์พุท Y 0 0 ปิด บน 1 0 1 ปิด บน 1 1 0 ปิด บน 1 1 1 บน ปิด 0 ประตู CMOS NOR

ถึง ข ย 0 0 1 0 1 0 1 0 0 1 1 0 การผลิต CMOS

อายุการใช้งานแบตเตอรี่ CMOS

อาการความล้มเหลวของแบตเตอรี่ CMOS

ลักษณะ CMOS

CCD กับ CMOS

ในบางแอพพลิเคชั่นเซ็นเซอร์ CMOS เพิ่งได้รับการปรับปรุงจนถึงจุดใดก็ตามที่พวกเขาบรรลุความเท่าเทียมกันใกล้เคียงกับอุปกรณ์ CCD โดยทั่วไปกล้อง CMOS ไม่แพงและมีอายุการใช้งานแบตเตอรี่สูงLatch-Up ใน CMOS

ข้อดี

TTL เป็นวงจรลอจิกดิจิตอลที่ทรานซิสเตอร์สองขั้วทำงานบนพัลส์ DC ลอจิกเกตของทรานซิสเตอร์หลายตัวมักประกอบด้วย IC ตัวเดียวข้อเสีย

แอพพลิเคชัน CMOS